# Michigan Technological University Digital Commons @ Michigan Tech

Dissertations, Master's Theses and Master's Reports

2018

### Modeling Data Center Co-Tenancy Performance Interference

Wei Kuang

Michigan Technological University, wkuang@mtu.edu

Copyright 2018 Wei Kuang

#### **Recommended Citation**

Kuang, Wei, "Modeling Data Center Co-Tenancy Performance Interference", Open Access Dissertation, Michigan Technological University, 2018.

https://doi.org/10.37099/mtu.dc.etdr/596

Follow this and additional works at: https://digitalcommons.mtu.edu/etdr

Part of the Systems Architecture Commons

#### Modeling Data Center Co-Tenancy Performance Interference

By

Wei Kuang

#### A DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

In Computer Science

MICHIGAN TECHNOLOGICAL UNIVERSITY

2018

© 2018 Wei Kuang

This dissertation has been approved in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Computer Science.

Department of Computer Science

DISSERTATION CO-ADVISOR: Dr. Zhenlin Wang

DISSERTATION CO-ADVISOR: Dr. Laura E. Brown

Committee Member: Dr. Steven M. Carr

COMMITTEE MEMBER: Dr. Min Wang

Committee Member: Dr. Timothy Havens

DEPARTMENT CHAIR: Dr. Min Song

| Lı | ST C | FIG   | URES V                                                        | VΙ  |

|----|------|-------|---------------------------------------------------------------|-----|

| Lı | ST C | OF TA | BLES                                                          | IX  |

| Ρı | REFA | CE .  |                                                               | ΊΙΙ |

| A  | BSTF | RACT  |                                                               | ΧV  |

| 1  | Int  | 'RODU | CTION                                                         | 1   |

|    | 1.1  | PRED  | CTING CONTENTION FOR DIFFERENT ARCHITECTURES WITH REGRESSIONS | 2   |

|    |      | 1.1.1 | Modeling sensitivity and pressure with regression             | 2   |

|    |      | 1.1.2 | CROSS-ARCHITECTURE PERFORMANCE MODELING WITH POLYNOMIAL CURVE |     |

|    |      |       | FITTING                                                       | 3   |

|    | 1.2  | IMPRO | VING PREDICTION ACCURACY USING CLUSTERING                     | 4   |

|    | 1.3  | PRED  | CTING PERFORMANCE FOR MORE THAN TWO CORE CO-RUN SCENARIOS     | 4   |

|    | 1.4  | Disse | RTATION ORGANIZATION                                          | 5   |

|    | 1.5  | Summ  | ARY OF CONTRIBUTIONS                                          | 6   |

| 2  | Вас  | CKGRO | UND AND RELATED WORK                                          | 7   |

|    | 2.1  | Mode  | LING CONTENTIONS FOR SHARED RESOURCES                         | 7   |

|   |     | 2.1.1  | SCHEDULING OR MODELING VARIOUS CONTENTIONS WITH OFF-LINE OR ON- |    |

|---|-----|--------|-----------------------------------------------------------------|----|

|   |     |        | LINE PROFILING                                                  | 7  |

|   |     | 2.1.2  | Modeling various contention with machine learning techniques .  | 31 |

|   | 2.2 | Масн   | INE LEARNING: CLUSTERING AND REGRESSIONS                        | 34 |

|   |     | 2.2.1  | HIERARCHICAL CLUSTERING                                         | 35 |

|   |     | 2.2.2  | PARTITIONING RELOCATION CLUSTERING                              | 36 |

|   |     | 2.2.3  | OTHERS: GRID-BASED CLUSTERING                                   | 38 |

|   |     | 2.2.4  | REGRESSION                                                      | 39 |

|   |     | 2.2.5  | PERFORMANCE MODELING USING MACHINE LEARNING                     | 41 |

|   | 2.3 | PERFO  | DRMANCE MONITORING AND BINARY INSTRUMENTATION                   | 41 |

| } | Cro | OSS-AI | RCHITECTURE PERFORMANCE MODELING FOR TWO CORES                  | 45 |

|   | 3.1 | Вивв   | LE-UP APPROACH FOR PERFORMANCE DEGRADATION PREDICTION           | 45 |

|   | 3.2 | Syste  | CM FRAMEWORK                                                    | 47 |

|   |     | 3.2.1  | CROSS-ARCHITECTURE SENSITIVITY MODELS                           | 48 |

|   |     | 3.2.2  | CROSS-ARCHITECTURE PRESSURE MODELS                              | 49 |

|   | 3.3 | Cross  | S-ARCHITECTURE PREDICTION                                       | 49 |

|   | 3.4 | EVALU  | JATION SETTINGS AND EXPERIMENTAL RESULT                         | 51 |

|   |     | 3.4.1  | HARDWARE ARCHITECTURES                                          | 51 |

|   |     | 3.4.2  | Training and test benchmarks                                    | 51 |

|   |     | 3.4.3  | SENSITIVITY CURVES AND REGRESSION MODELS                        | 52 |

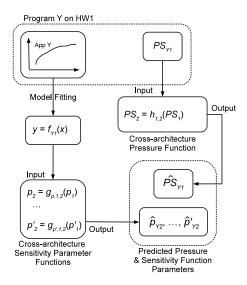

|   |     | 3.4.4  | MODEL SELECTION CRITERIA                                        | 53 |

|   |     | 3.4.5  | SELECTION OF SENSITIVITY FUNCTION MODEL                                     | 55  |

|---|-----|--------|-----------------------------------------------------------------------------|-----|

|   |     | 3.4.6  | Cross-architecture predictions for sensitivity curves                       | 56  |

|   |     | 3.4.7  | CROSS-ARCHITECTURE PREDICTIONS FOR PROGRAM PRESSURE                         | 57  |

|   |     | 3.4.8  | Cross-architecture co-tenancy performance prediction                        | 60  |

| 4 | Cro | OSS-AI | RCHITECTURE PERFORMANCE MODELING WITH CLUSTERING                            | 67  |

|   | 4.1 | REASO  | ONS FOR PREDICTION ERRORS AND HOW WE TACKLE THE PROBLEM WITH A              |     |

|   |     | K-ME.  | ANS CLUSTERING ALGORITHM                                                    | 67  |

|   | 4.2 | EVALU  | UATION SETTINGS AND EXPERIMENTAL RESULTS                                    | 73  |

| 5 | Ры  | RFORM  | MANCE MODELING FOR MORE THAN TWO CORES                                      | 83  |

|   | 5.1 | SCALA  | ABILITY ISSUES FOR CROSS-ARCHITECTURE MODELING FOR CONTENTIONS              | 83  |

|   | 5.2 | Prog   | RAM-SPECIFIC BUBBLE DESIGN                                                  | 86  |

|   | 5.3 | IDENT  | TIFY CRITICAL CODE SEGMENTS WITH INSTRUMENTATION                            | 88  |

|   |     | 5.3.1  | Identify instruction miss/hit last level cache the most $\ \ldots \ \ldots$ | 88  |

|   |     | 5.3.2  | Profiling access behavior of last level related instructions                | 91  |

|   | 5.4 | Bubb   | LE CREATION USING INSTRUMENTATION RESULTS                                   | 94  |

|   |     | 5.4.1  | CASE STUDY: SOPLEX                                                          | 94  |

|   |     | 5.4.2  | CASE STUDY: LIBQUANTUM                                                      | 98  |

|   |     | 5.4.3  | CASE STUDY: LBM                                                             | 100 |

|   |     | 5.4.4  | CASE STUDY: MCF                                                             | 101 |

|   | 5.5 | Evalu  | JATION FOR PERFORMANCE PREDICTION USING NEW BUBBLES                         | 106 |

|   |     | 5 5 1  | PREDICTION USING BURBLES ALONE                                              | 135 |

|   |       | 5.5.2 | PRED   | ICTIO | N WI | ΓH A | MI | XTU | JRE | OF | BU | BBI | ES | AN | D A | N. | ACI | rua | L I | PR | OG1 | RA. | M | <br>136 |

|---|-------|-------|--------|-------|------|------|----|-----|-----|----|----|-----|----|----|-----|----|-----|-----|-----|----|-----|-----|---|---------|

| 6 | Co    | NCLUS | SION . |       |      |      |    |     |     |    |    |     |    |    |     |    |     |     |     |    |     |     |   | <br>153 |

|   | 6.1   | Cont  | RIBUTI | ONS . |      |      |    |     |     |    |    |     |    |    |     |    |     |     |     |    |     |     |   | <br>153 |

|   | 6.2   | Futu  | RE WOI | RK    |      |      |    |     |     |    |    |     |    |    |     |    |     |     |     |    |     |     |   | <br>154 |

| В | IBLIC | OGRAF | РНҮ .  |       |      |      |    |     |     |    |    |     | •  |    |     |    |     |     |     |    |     |     |   | <br>155 |

| A | Co    | PYRIG | HT DO  | OCUM  | IENT | ΉΤΙ  | ON |     |     |    |    |     |    |    |     |    |     |     |     |    |     |     |   | <br>173 |

## LIST OF FIGURES

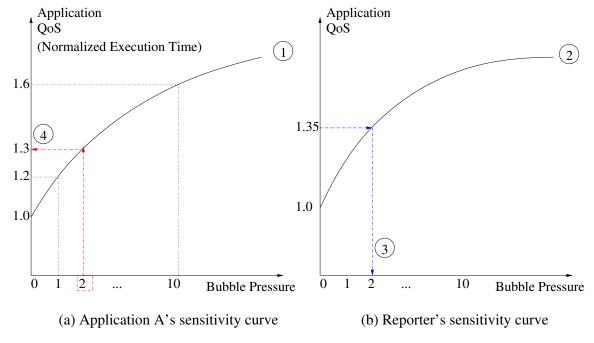

| 3.1 | BUBBLE-UP APPROACH TO PREDICT CO-RUN PERFORMANCE DEGRADATION                    | 46 |

|-----|---------------------------------------------------------------------------------|----|

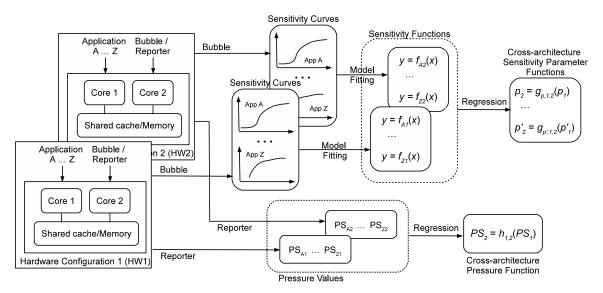

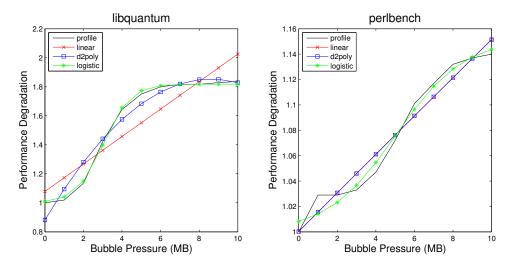

| 3.2 | DEVELOPMENT OF CROSS-ARCHITECTURE PREDICTION MODELS FOR SENSITIVITY             |    |

|     | PARAMETERS AND PRESSURE                                                         | 47 |

| 3.3 | USE OF CROSS-ARCHITECTURE PREDICTION MODELS                                     | 50 |

| 3.4 | Sensitivity curves for libquantum and perlbench fitted to regression models     | 53 |

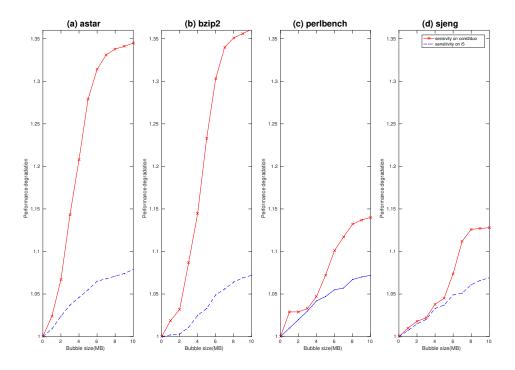

| 4.1 | Cross architecture sensitivity curve for (a) astar, (b) bzip2, (c) perlbench,(i | o) |

|     | SJENG ON CORE2DUO AND I5                                                        | 68 |

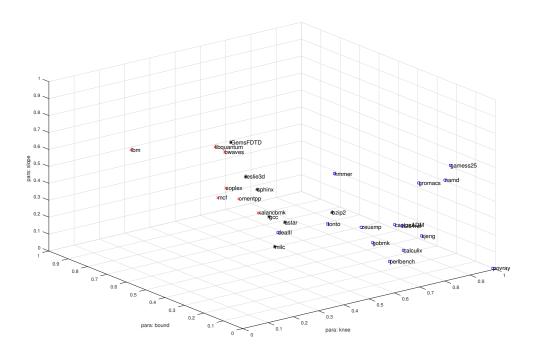

| 4.2 | LOGISTIC PARAMETERS DISTRIBUTION                                                | 75 |

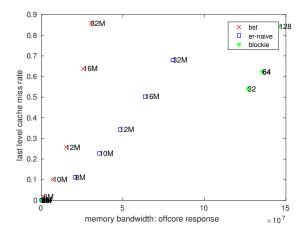

| 4.3 | SMASHBENCH KERNEL DISTRIBUTION                                                  | 79 |

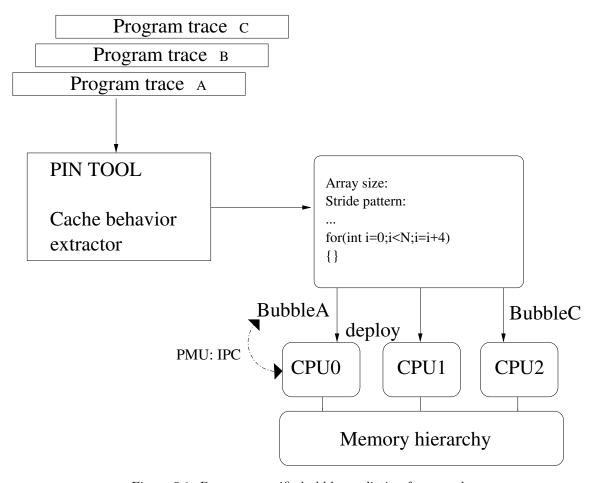

| 5.1 | Program-specific bubble prediction framework                                    | 87 |

## LIST OF TABLES

| 3.1  | HARDWARE CONFIGURATIONS OF EXPERIMENTAL MACHINES                        | 51    |

|------|-------------------------------------------------------------------------|-------|

| 3.2  | $R^2$ for SPEC06int models on Core2 Duo and Intel 15                    | 55    |

| 3.3  | RMSE value for SPEC06int models on Core2 Duo and Intel 15               | 56    |

| 3.4  | $AIC_C$ value for SPEC06int models on Core2 Duo and Intel 15            | 57    |

| 3.5  | MEAN ERRORS OF CROSS-ARCHITECTURE SENSITIVITY CURVE PREDICTION FOR IN-  |       |

|      | TEL I5 ON SPEC06                                                        | 58    |

| 3.6  | MEAN ERRORS OF CROSS-ARCHITECTURE SENSITIVITY CURVE PREDICTION FOR IN-  |       |

|      | TEL I5 ON TEST BENCHMARKS                                               | 59    |

| 3.7  | MEAN RELATIVE ERRORS OF CROSS-ARCHITECTURE SENSITIVITY CURVE PREDICTION |       |

|      | FOR INTEL XEON, 17, AMD A8 AND A10 ON SPEC06                            | 62    |

| 3.8  | BENCHMARK PROGRAMS PRESSURES ON DIFFERENT HARDWARE CONFIGURATIONS .     | 63    |

| 3.9  | Co-tenancy performance degradation prediction error on training (SPEC   | 06int |

|      | AND TEST BENCHMARKS                                                     | 64    |

| 3.10 | DETAILED PERFORMANCE DEGRADATION PREDICTION ERROR USING PREDSENS+PS     |       |

|      | AGAINST SPEC INT06                                                      | 65    |

| 3.11 | DETAILED PERFORMANCE DEGRADATION PREDICTION ERROR USING PREDSENS+PS     |       |

|      | AGAINST SPEC FP06                                                       | 66    |

| 4.1  | LBM PRESSURE CHANGES WITH DIFFERENT PEER CO-RUNNER                      | 71    |

| 4.2  | SENSITIVITY PREDICTION FOR DIFFERENT MACHINES                           | 73    |

| 4.3  | SPEC2006 CLUSTERING RESULT USING SENSITIVITY AS INPUT                   | 74    |

#### LIST OF TABLES

| 4.4  | Sensitivity prediction from c2 to i5 using cluster                     | 76   |

|------|------------------------------------------------------------------------|------|

| 4.5  | Sensitivity prediction from c2 to i5 using cluster extra               | 80   |

| 4.6  | Cross architecture sensitivity prediction for different machines w/o   |      |

|      | CLUSTERING                                                             | 80   |

| 4.7  | Cross architecture sensitivity prediction for different machines w/o   |      |

|      | USING 3 CLUSTERS                                                       | 81   |

| 4.8  | PERFORMANCE DEGRADATION PREDICTION FOR I5 USING CLUSTERING             | 81   |

| 4.9  | PERFORMANCE DEGRADATION PREDICTION FOR I5 USING CLUSTERING             | 81   |

| 4.10 | PERFORMANCE DEGRADATION PREDICTION ORIGINAL VERSUS CLUSTER-BASED METHO | D 82 |

| 5.1  | SPECCPU06 BENCHMARK PROGRAMS SOLO EXECUTION HARDWARE STATISTICS        |      |

|      | FOR INTEL 17                                                           | 108  |

| 5.2  | Clustering of programs based on hardware statistics                    | 109  |

| 5.3  | PREDICTION USING BUBBLES ONLY VS PROGRAM+BUBBLES                       | 136  |

| 5.4  | Prediction using bubbles only vs program+bubbles (continue)            | 137  |

| 5.5  | PERFORMANCE DEGRADATION PREDICTION USING SPECIFIC BUBBLES FOR MORE     |      |

|      | THAN TWO CORES CO-RUN SCENARIO                                         | 143  |

| 5.6  | PERFORMANCE DEGRADATION PREDICTION USING GCC BUBBLE FOR THREE-CORE     |      |

|      | CO-RUN SCENARIO                                                        | 144  |

| 5.7  | Performance degradation prediction using GCC bubble for $2/3/4$ core   |      |

|      | CO-RUN SCENARIO                                                        | 144  |

| 5.8  | PERFORMANCE DEGRADATION PREDICTION USING MCF BUBBLE FOR 3 CORE CO-RUN  |      |

|      | SCENARIO                                                               | 145  |

| 5.9  | Performance degradation prediction using BZIP2 bubble for $3/4$ core   |      |

|      | CO-RIIN SCENARIO                                                       | 146  |

#### LIST OF TABLES

| 5.10 | PROGRAM PERFORMANCE DEGRADATION PREDICTION USING ASTAR BUBBLE FOR     |     |

|------|-----------------------------------------------------------------------|-----|

|      | 3/4 core co-run scenario                                              | 147 |

| 5.11 | PERFORMANCE DEGRADATION PREDICTION USING PROGRAM SPECIFIC BUBBLES FOR |     |

|      | THREE-CORE CO-RUN SCENARIO                                            | 148 |

| 5.12 | Performance degradation prediction using sphinx3 and dealII bubbles   |     |

|      | FOR 3 CORE CO-RUN SCENARIO                                            | 149 |

| 5.13 | PERFORMANCE DEGRADATION PREDICTION USING SPHINX3 AND NAMD BUBBLES FOR |     |

|      | THREE-CORE CO-RUN SCENARIO                                            | 150 |

| 5.14 | PERFORMANCE DEGRADATION PREDICTION USING LESLIE3D AND GEMSFDTD BUB-   |     |

|      | BLES FOR THREE-CORE CO-RUN SCENARIO                                   | 151 |

| 5.15 | PERFORMANCE DEGRADATION PREDICTION USING SPECIFIC BUBBLES FOR FOUR-   |     |

|      | CORE CO-RUN SCENARIO                                                  | 152 |

### PREFACE

Author contribution statement: A partial content in Chapter 1 and the Chapter 3 in this dissertation uses contents from a published conference paper [61] by the author. The author conducted all the experiments and both advisors, Dr. Zhenlin Wang and Dr. Laura Brown provided advices on the work and they are fully aware that the work is reorganized and written in this dissertation. For a detailed acknowledgement of the permission granted by the holder of the conference paper copyright, please see Appendix.

### ABSTRACT

A multi-core machine allows executing several applications simultaneously. Those jobs are scheduled on different cores and compete for shared resources such as the last level cache and memory bandwidth. Such competitions might cause performance degradation. Data centers often utilize virtualization to provide a certain level of performance isolation. However, some of the shared resources cannot be divided, even in a virtualized system, to ensure complete isolation. If the performance degradation of co-tenancy is not known to the cloud administrator, a data center often has to dedicate a whole machine for a latency-sensitive application to guarantee its quality of service. Co-run scheduling attempts to make good utilization of resources by scheduling compatible jobs into one machine while maintaining their service level agreements. An ideal co-run scheduling scheme requires accurate contention modeling. Recent studies for co-run modeling and scheduling have made steady progress to predict performance for two co-run applications sharing a specific system. This thesis advances co-tenancy modeling in three aspects. First, with an accurate co-run modeling for one system at hand, we propose a regression model to transfer the knowledge and create a model for a new system with different hardware configuration. Second, by examining those programs that yield high prediction errors, we further leverage clustering techniques to create a model for each group of applications that show similar behavior. Clustering helps improve the prediction accuracy of those pathological cases. Third, existing research is typically focused on modeling two application co-run cases. We extend a two-core model to a three- and four-core model by introducing a light-weight micro-kernel that emulates a complicated benchmark through program instrumentation. Our experimental evaluation shows that our cross-architecture model achieves an average prediction error less than 2% for pairwise co-runs across the SPECCPU2006 benchmark suite. For more than

#### ${\bf ABSTRACT}$

two application co-tenancy modeling, we show that our model is more scalable and can achieve an average prediction error of 2-3%.

### Introduction

Today's computation has been continuously moved into the Cloud. Data centers often employ thousands of heterogeneous modern machines, providing their customers with elastic, scalable, and affordable computing and storage services. A modern machine is typically multi-core or many-core and hence able to host multiple applications or virtual machines (VMs). Co-locating applications or VMs can help improving server resource utilization and reduce operating costs. Certain resources, such as disk and main memory, can be partitioned across VMs on the same machine. However, some shared resources, such as the last level cache and memory bandwidth, are often implicitly shared and cannot be easily partitioned. Interference due to shared resources contentions can lead to performance degradation, a typical problem resulting from co-tenancy.

If the performance impact of co-tenancy is not predictable for latency-sensitive applications where response time or throughput is critical, data centers often have to dedicate whole machines to guarantee QoS even when this would result in under-utilization of the machine. Recent studies in co-tenancy and data center scheduling have made steady progress toward scheduling co-run applications to guarantee the performance [25, 26]. However, there still lacks an accurate model that can predict co-run performance across machines of different architectures.

Modeling and predicting co-tenancy interference is critical for data center job scheduling and guarantees QoS. Recent studies rely on two metrics, *sensitivity* and *pressure*, to quantify co-tenancy interferences [70]. Sensitivity measures how an application's performance is affected by co-run applications. Pressure measures how much an application impacts the performance of co-run applica-

#### CHAPTER 1. INTRODUCTION

tions. This dissertation shows that sensitivity and pressure are both application- and architecturedependent. We propose a regression model that predicts an application's sensitivity and pressure

across architectures with high accuracy. Co-run performance degradation can be predicted accurately by using the models of sensitivity and pressure for the co-run applications. High-accuracy

co-run performance modeling enables a data center scheduler to guarantee the QoS of the applications. Yet we find some programs' performance degradation are difficult to predict using this

approach. Further study shows that cross-architecture patterns are different across different group

of benchmarks. Clustering is used to categorize programs and separate models are constructed for

each group to address the problem. Moreover, as there can be more than two cores sharing the last

level cache and memory bandwidth. Thus, co-tenancy is not limited to just the pairwise case. It

also includes the case for three cores and four cores. We propose a new micro-kernel design that accurately resembles actual applications in a co-run setting and can be used to model the performance

slowdown in a contended environment.

# 1.1 Predicting contention for different architectures with regressions

Models that use metrics such as sensitivity and pressure can predict pairwise co-run performance accurately. However, an application's sensitivity and pressure will change as the architecture configuration changes. Therefore, such metrics must be measured on a per architecture basis. To reduce the cost of profiling, we can model an application's sensitivity and pressure, both of which are architecture dependent, by employing machine learning techniques such as regression modeling.

#### 1.1.1 Modeling sensitivity and pressure with regression

The miss ratio curve is widely used in application characterization and serves as a heuristic for resource allocation, where the x-axis is the cache size assigned to the application and the y-axis is

its cache miss ratio. Program performance degradation with respect to different levels of co-runner pressure can also be depicted as a function similar to a miss ratio curve. Performance degradation is actually the "sensitivity" of a program towards various levels of contention, where the x-axis is the co-runner's pressure score and the y-axis is the performance degradation scaled by solo execution time. Different applications react differently towards pressure, therefore the shape of the sensitivity curve can be varied. We have tried several classes of regression functions to fit the curve, including a linear model, quadratic model and a logistic model. We find that a logistic model of the form  $\frac{c}{1+e^{-b(x-a)}}$  fits best across all benchmark programs with different shapes. Moreover, the parameters of the logistic function are easy to interpret. As for each co-running program, the performance degradation will reach a point where cache is saturated and will no longer decrease, and one of the parameter reveals this upper bound. On the contrary, the program will perform similarly as the solo execution cases without too much slowdown when co-runner's pressure is at a 'benign' range and will be sharply increased after a certain point. The second parameter depicts such inflection point. At last, the third parameter shows how fast is the slowdown towards pressure after the knee point. We use a synthetic program, which is a memory bubble that can inflate or deflate to imitate the last level cache contention, to profile each program's slowdown with the bubble pressure ranging from 0 to the size of last level cache. We then fit those sample points into a logistic function. The fitting accuracy across all the programs is over 99%.

## 1.1.2 Cross-architecture performance modeling with polynomial curve fitting

In order to learn and model how a program's sensitivity changes between different architectures, a training set of applications are profiled on both machines. To reduce the profiling cost, only representative applications are selected for profiling. We divide the SPEC CPU2006 benchmarks into training and testing sets, and profile all training programs on each machine. We use a logistic function

#### CHAPTER 1. INTRODUCTION

to represent the sensitivity curve of each program, from which three parameters are extracted. In order to capture the transition pattern of those logistic parameters from one machine to the other machine, we fit the mapping of each parameter across two different architectures into a quadratic function to create the cross-architecture model. We then profile the testing program set on one architecture to generate logistic functions as their sensitivity curves. Using the logistic function parameters as the input, we predict the parameters of the logistic functions for each testing program on the other architecture to make final performance degradation prediction. The average prediction error is within 2%.

#### 1.2 Improving prediction accuracy using clustering

The framework's performance depends significantly on how closely the bubble and reporters can resemble the actual programs. However, some programs are benign to each other and some programs are aggressive towards resources. A single micro kernel therefore cannot resemble every case. This results in modeling errors. Even though average prediction error is within 2%, certain programs have prediction errors around 10%. We examine the prediction procedure and find that programs can be clustered such that programs within a cluster share similar cross-architecture transition pattern while different clusters have different transition pattern. Therefore, we divided the programs into clusters based on their cache access behavior and construct a model for each cluster. With three clusters, the average prediction accuracy is improved and programs with high prediction errors are now have much more accurate prediction result.

# 1.3 Predicting performance for more than two core co-run scenarios

Co-run scenarios are not limited to only two cores. We move one step forward, aiming to solve the co-run prediction problem for more than two cores. We find there is a scalability limitation in our current approaches and propose using program-dependent bubbles to tackle this limitation. The merit of using sensitivity and pressure is to decouple the pairwise co-run performance prediction into a linear-solvable problem. However the profiling cost increases as the number of participating cores increases. Moreover, the combinations of co-run peers expand exponentially, making the approach infeasible in practice. The purpose of using a bubble is to provide a way to resemble the actual program, and the bubble comes with various pressure scores. Therefore, we need an additional step to measuring which one best mimics the actual application. However, we can eliminate the measuring process if we can design a program-specific bubble that perfectly resembles the actual application. Moreover, we can make predictions out of bubble-only co-run instead of program-bubble co-run by observing the hardware statistics of the bubble when it co-runs with other bubbles. We use Intel<sup>TM</sup>'s Pin tool to analyze memory-related behavior of each program, identify hot code segments in the source code, and use that information to direct new bubble design. The new bubble has the fine-grain property such that it behaves almost exactly as the actual program does whether co-runners are present or not. With the newly designed bubbles, we can predict multi-core (3 or 4) co-run degradation still within 2% error and eliminate the process of measuring program bubble score, which greatly reduces profiling time.

#### 1.4 Dissertation organization

The rest of this dissertation is organized as follows. In Chapter 2, we briefly cover relevant background knowledge and discuss related work. In Chapter 3, our cross-architecture co-tenancy contention performance modeling is presented. We will describe our implementation and experimental results. In Chapter 4, we investigate the lower prediction accuracy of some programs and show that clustering programs into different groups according their cache access behavior can significantly improve overall performance. In Chapter 5, we expand the framework into a more than two core

#### CHAPTER 1. INTRODUCTION

co-run scenario. We also analyze the access behavior of each SPEC CPU2006 benchmark program by using the Intel's Pin tool. By identifying the hot code segments, we create program-dependent bubbles, which duplicate the access behavior of an actual program. The program-dependent bubbles are then compared with the bubbles we use in Chapter 3 and Chapter 4. We demonstrate that the newly designed bubbles show a very similar behavior as the actual programs do and adapt well to the changes of peer runners so that the prediction error is still within 2%. We conclude this dissertation in Chapter 6 by summarizing contributions, discussing the limitations of our approach and possible future work.

#### 1.5 Summary of contributions

We make following contributions in this dissertation.

- A cross-architecture contention model that enables performance prediction on both source machine and target machine with different hardware configurations.

- A categorization of applications according to memory subsystem sensitivity and pressure.

Category-specific modeling improves the prediction accuracy of cross-architecture co-tenancy performance degradation.

- A contention prediction model for more than two core scenarios. We propose a new microkernel design method that accurately imitates actual applications in terms of memory subsystem accessing behavior.

### BACKGROUND AND RELATED WORK

#### 2.1 Modeling contentions for shared resources

Modern architectures contain multiple processors on a single die so that several tasks can run simultaneously on the chip. To provide a certain level of isolation, each core has a dedicated L1 and L2 cache. However, applications usually require larger memory space, and a shared last level cache and main memory hierarchy can guarantee such requirements. Contention exists as long as applications share some resources. A wise job scheduling scheme makes good utilization of resources while at the same time prevents significant performance degradation due to contentions. The studies focus on resource allocation for contention environment has been a hot topic in the area. On one hand, a significant amount of prior work focuses on performance modeling, such as cache miss ratio modeling, memory bandwidth consumption modeling, and overall performance slowdown modeling. On the other hand, a great portion of prior work focuses on how to schedule co-run applications based on on-line or off-line heuristics so that system utilization and QoS are both satisfied whereas quite a few studies focus on pinpointing the pathological portion of the code and make appropriate modifications to alleviate contention. Related works will be given in the following section.

## 2.1.1 Scheduling or modeling various contentions with off-line or on-line profiling

For a Von Neumann architecture, data is first loaded into memory and fetched by the CPU for computation. On-chip cache can store frequently accessed data for such that loading cached data is much faster than directly fetching it from main memory. Therefore the performance of an application

#### CHAPTER 2. BACKGROUND AND RELATED WORK

is strongly related to its cache hit/miss behavior. Early studies try to model how an application's cache miss ratio is affected by the cache size allocated to it. Mattson et al. [71] and Kim et al. [60] propose similar algorithms to calculate the cache miss ratio for a given cache size. The algorithm scans through the memory trace of a program and maintains a LRU stack, where the most recently used data is at top of stack and the least recently used data is at bottom. When a memory location is accessed, one can first calculate the distance between the accessed location and the top of stack, then move it to the top to ensure a LRU replacement policy. This distance can determine whether or not current access will be a hit, as data located at the bottom section of the stack might be evicted due to the limited cache size. In general, if the cache size is smaller than the reuse distance, the data access will be a miss, vice versa if the cache size is larger than the reuse distance for the hit case. Throughout the execution trace, one can collect such reuse distance information and build a histogram. And calculate the miss ratio to a specific cache size C by adding up all memory accesses whose stack distance is larger than C.

Recording a memory trace requires huge space, Bennett and Kruskal [6] find storing the last access of each memory access is enough to recover the reuse distance histogram, as all windows between a consecutive pair of last accesses have the same footprint and can be counted in a single step. Olken [79] improve the memory trace algorithm efficiency by organizing a simplified trace as a tree where each node stores the timing information of the data. However, as one tree node represents a unique memory access, the resulting tree can become huge in size. Approximate algorithm is introduced later to trim the tree. Zhong et al. [129] propose a scale tree, where each node represents a collection of datum. Each tree node has a time range attribute, and a size attribute, where the size indicates number of datum last accessed during the time range. A reuse distance histogram can be constructed from the scale tree where different reuse distance are grouped into bins so that the computational complexity can be reduced. Xiang et al. [113] improve the trace analysis algorithm

by dividing trace into c sub-intervals, where each interval has k distinct data. The complexity is  $O(ck \log m)$ , where m is the total data size of the program. In later study, Xiang et al. [114] propose a linear algorithm for analyzing a length n trace without considering the data size m. The algorithm measures the distribution of time distance of all data reuse, the first and last access of each distinct data by scanning through the trace once with a hash table implementation. The algorithm results in O(n) time complexity and O(m) space complexity with accurate average footprint for all execution windows of the trace. Using the footprint and reuse histogram, one can predict the miss ratio for difference cache size. However, as a program can accept input of different size, the miss ratio curves (MRC) obtained through profiling using a specific input can not direct cache allocation for the same program using a different size input. Zhong et al. [128] propose a way to predict the MRC for various input size using two profiling runs. The histogram of two different runs are divided into the same number of bins, where each bin contains same proportion of total access. This is based on presumption that the proportion of each class of reference remains the same for different inputs, which is experimentally hold for most programs tested. Then use a linear model and solve the parameters with data collected from two runs. After that, one can recover an accurate the histogram of references for any input size and further create MRC for a specific input. The model predicts the MRC for different input sizes within 1-2% error compared with the actual MRC collected from hardware performance monitoring units.

Berg and Hagersten [7, 8], Eklov and Hagersten [33], Eklov et al. [32] propose StatCache, which is another approximated algorithm to derive the MRC based on reuse distance. The original reuse distance is to count number of distinct memory accesses in-between two same memory references. Statcache constructs a probabilistic model of memory references and using this model to derive the reuse distance. Using a sample of 0.01% of memory references, experimental results show that the shape of reuse statistic of the sampled set is very similar to the reuse statistic that uses every single

#### CHAPTER 2. BACKGROUND AND RELATED WORK

memory access. In Shen [93, 92, 53]'s work, a similar probabilistic model is used to convert reuse time to an estimation of distinct memory references in-between two accesses of the same datum. The approximation accuracy is over 99% for cache block reuse and over 94% for element reuse, suggesting a strong connection between reuse time and reuse distance.

Reuse distance, footprint and miss ratio are related but the relationship between them is unclear. Ding et al. [115] revisit five metrics: footprint, the amount of data accessed during a time window; volume fill time, the average time a program access a given volume of data; inter-miss time, the average time between two cache misses; miss ratio, the fraction of references that cause a cache miss; and reuse distance, number of distinct memory access between current and previous access to the same datum. They demonstrate that those metrics can be derived from one another and verify the transformation through exhaustive testing. StatStack [34] employs the footprint theory and constructs MRC in linear time by converting reuse time to reuse distance. However, the space complexity of StatStack is O(M), where M is the distinct elements in the memory trace. For storage workloads, which can last for days or weeks, the space requirement is huge. Counter Stack [110] and SHARDS [106] are proposed to reduce the space complexity. Counter Stack uses a probabilistic model to approximate MRC with guaranteed accuracy while at the same time uses sub-linear space. SHARDS uses a splay tree to track distinct data, and both algorithms achieve low level space requirement. Hu et al. [46] propose an average eviction time (AET) model which can quickly construct MRC with very low cost. Moreover, the algorithm can characterize shared cache behavior using footprint theory by modeling each application in a co-tenancy group.

Above researches build a cache model based on application's memory access traces. It assumes that only one application is running with a specific cache configuration, which is true for early architectures that only have single CPU core on them. On one hand, different programs can be executed in a sequential order, one can predict the cache misses for each program based on its own

reuse distance analysis. On the other hand, programs can be executed in an interleave pattern, where all participating applications contribute to a memory access trace, single program trace analysis will fail to make accurate miss ratio prediction due to the interference.

Research on how a cache is affected by such interleave patterns has been done as early as 1980s [102]. Thiebaut and Stone [102] propose a probability model that can estimate the miss ratio if two programs A and B running on a core in an interleave pattern. Their model calculates the average number of occupations in cache  $N\bar{X}$  for A, the average number of A's occupations evicted when B takes over control  $N\bar{Z}$  and the average reload transient using A's footprint  $FP_A$  minus the difference between  $N\bar{X}$  and  $N\bar{Z}$ . Their model also suggests that for a smaller cache, smaller associativity tends to have a lower cache miss rate since the entries are more evenly distributed to each congruent class and are less likely to overflow the cache. When cache size is significantly larger than the footprint, the reload transient of a higher associativity cache is smaller than the reload transient of a lower associativity cache, as rows that receive several lines because of a larger associativity are truncated in cache with lower associativity. Thus the footprint is smaller for a cache with a smaller associativity. Modern architecture now provides hardware support such that the shared cache can be partitioned. Programs given sole access to a cache of optimized size can run with a few or even without performance degradation. However, the profiling and simulation process required to construct the MRC is time consuming. Even with on-line instrumentation tools, it still significantly slows the execution. An on-line method is proposed by Tam [99] to quickly construct the MRC for a given program with only several hundreds milliseconds. The approach records only L1 data cache misses, which will become data accesses to L2 cache. With only a short burst of time during execution, the PMU records a memory trace and the reuse histogram is built from this trace. The MRC generated from the trace using the approaches described by Mattson et al. [71] can be used to direct cache partitioning for pair-wise co-run program groups. To be specific, suppose the MRC

#### CHAPTER 2. BACKGROUND AND RELATED WORK

for program A and B are  $MRC_A$  and  $MRC_B$ , total shared cache size is C, the solution is to find the cache size x, and C-x, such that  $MRC(x)_A + MRC(C-x)_B$  are minimized. As is mentioned above, one cannot use single program reuse distance analysis to predict the situation in a contention scenario. For example, Xiang et al. [115] show experimentally that the estimation of miss ratio of corun pair cannot be done through simple summation of individual miss ratio. However, the footprint is linear composable, and the group miss ratio can be derived from the group footprint, which can direct the co-scheduling of jobs on a multi-core architecture. Wang et al. [109] adopt higher order of locality theory [115] and explore symbiosis scheduling through on-line sampling. They propose an on-line based approach to quickly construct the group MRC. Their approach has a trade-off between sampling frequency and model accuracy. Adaptive burst footprint (ABF) sampling is employed in this paper. By setting up the threshold h, the sampling frequency is calculated each time such that it is long enough to measure the miss ratio greater than or equal to h. Moreover, by setting up the ratio between sampling and non-sampling interval, the overall cost of sampling is bounded, usually below 1% of the overall execution time of actual program. With accurate miss ratio prediction based on locality analysis, the MRC is a quantitative measurement for cache contention and can be used as a heuristic to direct job scheduling. However, the relationship between miss ratio and performance degradation is unclear. In [82], two metrics are given to depict the effect of cache on execution time. In fact, Sun et al. [98] show that a significant portion of the performance slowdown comes from the events unrelated to CPU and cache. Rather the memory controller, memory bus and DRAM modules cause significant slowdown, as contention on memory bandwidth can affect performance by increasing memory access latency and decreasing memory bandwidth [67]. This suggests that a memory bandwidth consumption model might be more accurate in directing co-tenancy scheduling over cache miss ratio model. Tools such as Cache Pirating [35] and Stressmark [116] can plot similar performance metrics such as CPI as a function of allocated cache size, and can be used to quantify

the relationship between performance and memory bandwidth consumption in a contention scenario.

Yan [20] propose a profiling based approach to predict inter-thread cache contention on a CMP architecture. The MRC, with respect to different cache size, can be obtained through stack distance profiling. For a given cache size, one can estimate the cache miss rate. The authors present three methods to model cache miss prediction based on following: frequency of access (FOA) model, stack distance competition (SDC) model and a probabilistic model. The FOA model suggests that as programs co-run on a multi-core system can run at different pace in terms of cache access speed. Thus, one can estimate a program's effective cache size by calculating the proportion of its own access speed over the overall access speed. This can be problematic since programs co-run together can have different stack position shapes and reuse frequencies. The SDC model merges individual stack distance profiling into a combined one and calculates the winner at each stack position. After profiling, one can calculate the effective cache size based on this newly created, combined stack position information. The probabilistic model considers ones step further. Previous methods build on the assumption that an access will always be a hit as long as the reuse distance is less than given cache size. However, even the access of a most recent use can become a miss if there are enough misses introduced by other process. Thus the probabilistic model considers the probability an access will turn from a hit into a miss. They test this model on a CMP machine with 14 pairs of co-run groups. Experimental result show that the model prediction error is within 3.8%.

Xu, Chen, Dick, and Mao [116] propose the CAMP framework, which uses reuse distance histograms, cache access frequencies, and the relationship between the throughput and cache miss rate of each program to predict the effective cache size and instruction throughput estimation (IPC) when running concurrently and sharing cache with other programs. The merit of this method is that it requires no off-line profiling, operating system modification and additional hardware support. CAMP calculates the effective cache size of programs running in a contention memory subsystem

#### CHAPTER 2. BACKGROUND AND RELATED WORK

at a steady state, and treats non-repeating phases separately. To be specific, given a carefully designed stress-mark (micro-kernel benchmark) which can be tuned to have a specified effective cache size, CAMP co-runs the stress-mark with some program P several times with different effective cache sizes. CAMP constructs the probability of effective cache sizes of program P using various performance statistics such as miss per access and further derives reuse distance. With the performance degradation curves for various cache size and effective cache size of the program in a specific co-run groups, one can predict the program's performance degradation. A similar approach is given by Mars et al. [70]. On-line profiling of the reuse distance can reveal how much proportion of cache each contention peer can occupy. CAMP is tested on a two-core CMP machine, with 55 different combination of SPEC CPU2000 benchmark programs. The average prediction accuracy is 1.57%. Performance degradation results not only from cache contention but also congestion at off-chip memory hierarchy. Quite a few works focus on mitigating contentions by memory request scheduling [4, 58, 59] or using memory channel partitioning [51] or interleaving jobs to alleviate interference [55]. Only a few researches focus on actual performance modeling. Riseman et al. [85] observe that the number of instructions that can be issued per cycle is approximately the square root of number of instructions in the window. Michaud et al. [73] also come up with power-law relationship, which is essentially a square-root conclusion. This conclusion is later used for modeling basic/sustained CPI [54, 39, 40], followed by building up the model for miss-event penalty, including branch mis-prediction, instruction-cache miss and data-cache miss. Van Craevnest et al. [105] use similar stack idea but predict program performance changes when migrating it from a small (big) core to a big (small) core. The performance (CPI) is divided into two parts, base component and memory component. Base component is used to model instruction level parallelism (ILP) changes when migrating and memory component is used to model memory level parallelism (MLP) changes when migrating.

Eklov et al. [36] propose the Bandwidth Bandit to characterize how an application's performance is effected when memory bandwidth is decreased. The bandit engine co-runs with a target application and monitors the target's CPI while keeps increasing memory bandwidth consumption. The bandit engine is essentially a carefully designed micro-kernel that can inflate or shrink in terms of its memory bandwidth usage, we will use similar concept such as bubble and pirate interchangeably in this dissertation to refer such probing kernel. The bandit manages to only stress memory bandwidth without touching other shared resources. By running the bandit kernel at a specific rate in a controlled manner, the target application's performance changes due to contention for off-chip memory resources alone can be quantified. To obtain the memory access latency for 3 different types, which are page-hit, page-empty and page-miss, another carefully designed micro-kernel is run on the target architecture, this program traverses a link-list, where each access is dependent on previous access. Therefore, manipulating the layout of such link-list ensures the latency of a desired event can be recorded.

Subramanian et al. [97] focus on modeling performance degradation of memory bound programs in a contention environment. They observe that the slowdown of a memory bound application is linear proportional to the memory request service rate. Therefore the slowdown can be estimated by using the solo run memory request service rate divided by application's co-run memory request service rate can be directly observed on the fly when it runs in an contention environment. The application's solo run memory request service rate can be estimated by assigning the program with the highest priority in accessing memory. For non-memory bound programs, which spend significant amounts of time performing computation, a parameter  $\alpha$  is introduced which is calculated by ratio between the number of cycles stalled because of memory request and total number of cycles elapsed. These statistics can be obtained through PMU. Subramanian et al. [96] propose application slowdown model (ASM) in a follow up

#### CHAPTER 2. BACKGROUND AND RELATED WORK

study. Prior studies assume an application's sole execution information is known and create a model to predict the slowdown in a contention scenario. In this study, programs are already running in a contended environment, and one must instead predict its sole execution time to calculate the slowdown, so that the progress information can be used for a fairness-aware scheduling scheme. They find that program performance is strongly related to its access rate to the shared cache. Therefore, slowdown prediction is reduced to estimating a program's access rate to the memory subsystem. Estimation of sole execution information is a two step process. The first step is to minimize memory bandwidth contention by assigning the request from a program of interest with highest priority at memory controller periodically. The second step is to quantify shared cache contention by using an auxiliary tag store to estimate cache misses due to contention. The auxiliary tag directory (ATD), first proposed by Qureshi and Patt [84], is a way to quantify utilization of shared cache and direct scheduling according to that metric. Du Bois et al. [28] propose PTCA, which make use such structure and estimate cache hit and miss for a sole execution using a co-run profiling result. Similar work also found in Ebrahimi et al. [30].

To predict the performance of memory bound applications, the application access pattern should be considered. However, as memory accesses issued from CPU cores are filtered by the private L1 cache and shared last level cache, it is extremely difficult to capture accurate off-chip memory access behavior. Instead, DRAM commands generated by the memory controller can be examined to derive the memory access pattern [22]. Moreover, as the minimum time delay depends on different cases of DRAM command pairs, the bank busy time is modeled as weighted summation of those different cases of minimum time delays, and the weight is determined by the frequency of occurrence for such pairs during program execution. Gulur et al. [44] propose ANATOMY, which uses a three stage queue model to evaluate memory performance, including the command bus, memory bank and data bus. The average memory request latency can be calculated as the summation of

queuing delay and service time for all three stages. Wang et al. [107] consider multiple factors in predicting the memory bandwidth consumption of programs in a contention environment. They propose two models: Dramon-T and Dramon-R. Dramon-T is a memory trace based implementation for bandwidth usage prediction. To estimate bandwidth consumption, Dramon-T considers both program memory request rate and memory request service rate. Memory request rate prediction is reduced to program request issue rate prediction, which is limited by the program behavior, and DRAM service rate, which is limited by memory contentions. Memory request rate is reduced to calculating the reciprocal of average memory request latency, which is further reduced to estimation of memory request hit, miss, conflict ratios as these 3 cases will have different latency. Then a probabilistic model is used to predict if an arbitrary request is a hit, miss or conflict. Dramon-R is on-line bandwidth prediction model using PMU readings as input. Thus the probabilistic model can be replaced by hardware statistics. Both model achieve high prediction accuracy over 95% on portable benchmark proposed by McVoy and Staelin [72].

Sandberg et al. [87] make an interesting analogy of the cache behavior of two contended applications. As it can be viewed as two flow of liquid filling a glass. The liquids which overflow the glass correspond to the data evicted by the cache due to the replacement policy, and the concentration of each liquid inside the glass is proportional to its inflow rate. By this analogy, one may predict performance using each application's fetch rate and data reuse pattern and knowledge of how these factors change due to contention. In a steady state, the amount of program data evicted by the cache should equal the amount of program data fetched by the cache, which in other words, the replacement rate is equal to the fetch rate. If the replacement is random, the probability of replacement is proportional to the amount of cache allocated to the application. Cache pirating can generate the function needed. To be specific, an application's miss rate, fetch rate, hit rate, miss ratio, etc. as a function of cache size can be obtained through cache pirating. Many performance modeling consider

average slowdown of a program when it co-run with other applications. However, programs are not always perfectly aligned and they can have phases that exhibit significantly different behavior, using average can be misleading and result in high prediction errors. In Sandberg et al. [88] follow up work, phase detection [29, 89] is employed to generate contention prediction model at a refined granularity. Programs in execution are divided into slices and the prediction model is applied to every slice. To reduce overhead, a dynamic window combines all slices within a phase together and apply the prediction model only once. To further speed up the process, the predicted slowdown of two specific phases from two applications can be cached and reused whenever the same pattern occurs again. This fine-grained prediction model results in average prediction error of 0.41% and maximum prediction error of 1.8%.

Mars et al. [70] propose "bubble-up" as an approach for tackling the contention prediction problem. Their approach relies on thorough off-line profiling of programs' reaction toward pressures. For a two core co-run scenario, for optimal scheduling, an oracle scheduler must obtain the performance degradation of all possible pairs-wise slowdowns, which results in a  $O(n^2)$  time complexity. The framework decouples the pairwise performance prediction problem into measurement of sensitivity and pressure of each individual programs, thus lowering the complexity to O(n) as oppose to  $O(n^2)$ with brute force. By combining one program's sensitivity toward pressure and a co-run program's pressure score, the performance degradation of co-run group can be identified. Experimental result show that the prediction accuracy is within 2% for co-run groups randomly generated from the SPEC CPU2006 benchmark suite. A follow up paper proposes "bubble-flu" [120], which utilizes the bubble up methodology for coarse scheduling, and at the same time utilizes on-line profiling to monitor IPC changes. And the bubble-flux engine calculates the ratio between running and pausing of a program if the group performance degradation violate the QoS requirement as a finer adjustment strategy.

"Bubble-up" creates a performance model with respect to contentions which happen at memory

subsystem as a whole. Eyerman et al. [38] introduces the idea of a speedup stack to describe how a program's performance is affected by a stack of factors such as on-chip cache contention and off-chip memory bandwidth consumption. Eklov et al. adopt the idea and use cache pirating [35], a technique similar to bubble [70] to create speedup stack models [37]. Their pirate kernel is carefully designed such that the fetch rate is close to zero so that this probe-kernel always stays in cache when it co-runs with a program of interest. Therefore it can extract the effect of cache contention from memory bandwidth contention, since program of interest will compete for cache with the pirate kernel but exclusively use memory bandwidth. Moreover, for a system with cache size C, one can run n copies of a program together, thus each program will actually receive C/n cache size in a stable state. As these instances will compete for off-chip memory bandwidth, one can compare the hardware statistics collected from this scenario with the one using cache pirating to extract the memory bandwidth factor for the speedup stack model.

Zhao et al. [125, 124] distinguish SPEC CPU2006 programs into three categories, cache-bound, memory-bound and cache/memory-bound, by plotting cache miss and memory bandwidth consumption metrics. The authors use a series of contention models, each representing one shared resources, to obtain the performance degradation through the aggregate pressure on these resources. For each program  $A_i$  being characterized, first pick three co-runners to form a four core co-run group, and use performance metrics to collect each program's individual pressure on cache and memory bandwidth. Then run them as a group and record program  $A_i$ 's slowdown, therefore, one sample point is collected as a mapping of aggregate pressure and slowdown. A training set is constructed from 200 co-run group executions (all including program  $A_i$ ). As the theoretical memory bandwidth is known in advance, the memory consumption range is then divided into three pieces to represent cache-bound, memory-bound and cache/memory bound cases. Therefore, the training data falls into one of the three categories based on their aggregate memory bandwidth consumption, from which a piecewise

model is created. The overall approach is a two phase process. In the first phase, a collection of programs are selected and trained to determine the piecewise function, with the parameters undetermined. The second phase is to instantiate a model with application-specific parameters, using the abstraction model yielded by phase one as a candidate regression model, and collect the slowdown for only a small subset of co-run program to solve the parameters. The prediction error ranging from 0 to 10.2%, with a average value of 0.1%.

In de Blanche and Lundqvist [24], four performance degradation prediction models are compared, which are one slow-down based, two contention-based and one memory bandwidth consumption based methods. These methods, use the similar idea by running programs with "bubble" on shared resources multiple times to acquire sensitivity and pressure. The slowdown-based method "Memgen" performs better than other methods, and memory bandwidth consumption based method can also match the performance of "Memgen", suggesting that using memory bandwidth, or performance as a whole, is better than using cache miss rate as a metric or heuristic in co-scheduling prediction tasks.

The above studies provide quantitative methods to measure application performance whenever contention presents. Other studies focus on characterizing the type of contention and use this information as a heuristic to direct co-tenancy scheduling.

Focusing on the co-tenancy scheduling problem, Snavely and Tullsen [94] introduce "symbiosis" as a performance metric composed of three parameters: 'diversity', which describes whether or not all functional unit are running throughout execution; 'balance', which describes whether under-utilization will lower system efficiency and over-utilization will result in conflict and jeopardize performance; and 'conflicts', which describes how programs behave toward a shared resource. In their SOS framework, during a short sampling period, the permutation of all possible co-run groups are test on the system. The hardware counters monitor IPC, total conflicts on integer queue, floating point queue, .etc, L1 data cache hit rate, diverse of instructions, and a weighted sum score

of diversity, balance and conflict can be calculated for each candidate group and the one with best score is selected. With the help of SOS framework, a system with random job arrival and departure gains as much as 17% performance over a framework without symbiosis.

For characterizing the source of contention between threads of an application or between multiple applications, one straightforward way is to run application with dedicated resource first as the baseline reference, then co-run a group of applications together multiple times, letting them share one shared resources each time. The co-run cases are compared with baseline to determine if that particular resource is contented by the peer runners. In Dey et al. [27], Parsec 2.1, a multi-threaded benchmark suite is selected and the characterization of contention focuses on L1 cache, L2 cache and memory FSB. Hardware performance counters are used to quantify contentions and event UN-HALTED CORE CYCLES is selected to determine both intra and inter application contentions. The architectures used in the experiment have private L1 cache, and shared L2 cache for every two cores. Interestingly, the intra-application contention is not much for L1 and L2 cache; programs show performance improvement as they have data sharing. The contention on FSB result in performance degradation as there is an increase in memory bandwidth consumption by multiple threads. For inter-application contention, as different applications each access their own data, contention is prominent compared to the intra-application cases. Even though profiling contention over multiple applications is time consuming, characterization of applications provide significant information for scheduling.

Co-scheduling of jobs can result in contention, and with a smart scheduling scheme, the overall performance degradation due to such contention can be significantly reduced [52]. Some studies suggest using reactive scheduling, which is runtime trials, keep changing the co-runner of a program to record its performance degradation towards different peers and then schedules those programs that are benign to each other together. This method can serve as the base of an on-line, lightweight

scheduling algorithm. However, without knowing the optimal scheduling solution, it is hard to compare the reactive scheduling method with the optimal one, and whether or not there will be significant improvement if one scheduling adjustment is made. Other studies try to predict performance of programs when co-tenancy exists and with that knowledge one can pro-actively schedule programs by minimizing the overall co-run performance degradation. The paper [52] first demonstrates that such a scheduling problem can be solved in polynomial time if the group size is fixed to two, otherwise it is NP-complete problem. The authors give a scheduling scheme based on minimizing the pair-wise degradation weights of a graph and also gives several approximate scheduling schemes that can provide fast yet close to optimal scheduling options. The first scheduling scheme is a hierarchical perfect matching algorithm. It is derived from the solution of two core co-run problem. First solving the dual-core pair scheduling in polynomial time. Then creates a new degradation graph with each vertex representing co-run pairs in the first step and apply a minimum weight matching algorithm on the new graph to obtain the solution to a quad-core scheduling solution. To generalize the algorithm, one can approximate the optimal solution for the K core co-scheduling problem by applying the minimum perfect matching algorithm  $\log_2 K$  times. The second scheduling scheme uses a greedy algorithm. Note that for a naive greedy scheduling scheme, which first sorts all k-cardinality sets in ascending order of total degradation and always picks the minimum degradation group until the final solution covers every job, yields a poor scheduling result. The reason is clear, programs that generate less pressure are in-sensitive to pressure, and also benign to co-runners, are friendly applications. Thus, in a naive greedy algorithm, the top set is likely to contain friendly applications; after a while, this set is depleted as the scheduler has no choice but to pick jobs with aggressive memory behaviors. Therefore, a more reasonable greedy job scheduling algorithm is to first obtain the performance degradation of all k-tuple groups that contain each job, and sort the groups to get the 'politeness' of each job, then each time pick the co-run group with minimum degradation which contains the program with the current best politeness score while other programs in the co-run group has not yet been selected into the final scheduling set. This yields much better scheduling results as polite programs and unfriendly ones are scheduled together while at the same time total performance degradation is minimized.

The above study tried to use different grouping mechanisms to alleviate the effect of resource contention. Blagodurov et al. [11], Zhuravlev et al. [130] survey grouping mechanisms based on program behavior characterization, comparing these approaches and proposing both off-line and on-line solutions to the scheduling problem. There are three different grouping mechanisms discussed: the Stack Distance Competition (SDC) algorithm, the Animal class algorithm and the Pain algorithm. SDC is based on the profiling of the memory trace on a LRU cache. Rather than obtain the memory access (cache access) histogram of each individual program, one can monitor the access of two candidate co-run peers, decide who wins (cache hit) on a specific cache line position and mark the combined LRU stack position with the winner information. After multiple iterations, one can determine the effective cache size of each co-runner and make proper performance degradation prediction. The Animal class algorithm classifies programs into different categories in terms of their sensitivity towards contention. Turtle, sheep, rabbit and devil; these four types of animal categories are sorted in ascending order with respect to contention sensitivity. With stack distance profiling, one can put a program into the appropriate class and give each pair of animals a score, which serves as information for scheduling. Pain classification introduces the sensitivity and intensity of a program, where sensitivity depict how a program react towards pressure and intensity describe how much pressure a program can stress onto the shared resources. By combining the two metrics for a given co-run pair, one can calculate the pain score thus direct scheduling. Once again, the author make use of LRU stack distance profiling. At each stack position, one can associate a loss probability to indicate how likely a hit will become a miss when contention exists. Then scale the hit by the probability

to calculate extra misses to obtain the sensitivity score. Intensity is measured as last level cache accesses per million instructions as the measurement. Thus the Pain score for a program A when co-run with a program B is the product of A's sensitivity and B's intensity. The pair Pain score of program A and B is the sum of their Pain scores. Experimental result show that the Pain and the animal class algorithms perform well, as the performance degradation is only slightly worse than perfect scheduling. However, the SDC algorithm is only slightly better than a random scheduling scheme. It is possible that because the SDC algorithm doesn't consider the access speed of the two co-run peers, and only focuses on cache contention without considering other factors that will affect performance. The authors run a series of experiments to breakdown the factors that result in performance degradation, and discover that cache contention itself does have an effect on performance degradation, but sometimes contention for the memory controller, front-side bus (FSB), and prefetcher resources play dominant roles in performance degradation. They found that cache miss rate turns out to be a good heuristic for performance degradation prediction in a contention scenario. Though Pain classification delivers the best performance, it has certain complexity when stack distance is calculated on the fly. In contrast, using last level miss rate as heuristic is much simpler and yields slightly worse result. Based on those observations, the author implements two scheduling algorithms using miss rate as a scheduling heuristic. The first is Distributed Intensity (DI), which uses stack distance profiling to estimate last level cache misses, then use the last level cache miss estimation to make a classification. The second one is Distributed Intensity On-line algorithm (DIO), which is a user level implementation of DI with only on-line profiling of last level cache miss as the heuristic to direct classification. Experimental result suggest that the DIO algorithm is within 2% of the optimal scheduling solution.

Xu et al. [117] propose a scheduling mechanism based on balancing memory bandwidth contention. The situation is simplified as there is no shared cache on their testing platform. In selecting

a candidate job to be scheduled, traditional approach usually picks candidates using the following fitness function:

$$FITNESS^{P} = \frac{1}{\left|\frac{BW_{remains}}{CPU_{remains}} - BW_{required}^{p}\right|}$$

That is, the traditional approach always finds a job which maximizes the fitness function, which always finds the candidate job p, whose memory bandwidth requirement is as close to average memory bandwidth as possible. Experimental results show that performance degradation starts before the aggregated memory bandwidth reaches peak value. Thus an accurate  $BW_{remain}$  is necessary to make good scheduling decision, which in this paper, is estimated by Ideal Average Bandwidth. Ideally, programs run on a platform with infinite memory bandwidth. Those programs will run without contention, with finishing time idealturnaroundtime, which is the shortest time a program can finish its execution in a contention environment. The ideal average bandwidth is the ratio between the total number of memory accesses and the ideal turnaround time. Combined with the fitness function mentioned above, one can schedule a job whose combined memory bandwidth requirement is close to the Ideal Average Bandwidth. In other words, rather than targeting peak bandwidth utilization when scheduling a job, one should keep the total bandwidth requirement close to the ideal average bandwidth of the entire workload to avoid unnecessary contention. Feliu et al. [41] extends the idea to situations with multiple level of shared memory. They propose the PC-Degradation Cache-Hierarchy Contention-Aware Scheduler algorithm, which achieves almost double the average speedup compared with state of art memory-aware scheduling algorithms.

As memory contention has been identified as the main cause for system wide unfairness [76, 30, 77]. Xu et al. [118] propose a fair-progress scheduling (FPS) policy. FPS uses the PMU to monitor hardware statistics for programs being executed and derives forward progress throughout the scheduling quantum. To be specific, FPS monitors number of instructions a program has executed during the quantum, estimates the IPC of a program phase running alone during a time window of

quantum length, and calculates the ratio between them to obtain the progress. To maintain fairness, the policy always picks the program with the lowest progress value and lets them run during the next scheduling quantum. The policy improves overall system fairness but has a slight overhead in system throughput.

Different programs have different access speeds to cache, and the program with the fastest access speed usually places more pressure than programs with slower access rates. However, giving programs with fast access rate a larger cache size might not improve performance. For example, video streaming access programs visit cache fairly fast, but the data is unlikely to be accessed again. Qureshi and Patt [84] argue that one should allocate cache based on utilization rather than demand, that is, when a program's speedup stops increasing when the allocated cache size increases, one should not allocate more cache to the program. They categorize different programs into low utility, high utility and saturating utility based on how performance changes when allocated cache size increases. Hardware performance counters can collect statistics while programs compete for shared resources. However, the events are per-core based and cannot reflect the interactions between these applications. Zhao et al. [126] propose CacheScouts, which motivates a hardware design to better understand cache behaviors among contention peers. Counters and data structures are added to the cache and are associated with monitor identity so that one can learn cache occupancy and cache interference/share per application. To reduce overhead, only partial cache sets are tagged with counter/structure as one can still obtain accurate cache behavior through set sampling [56, 103]. The framework provides insight for future architecture design for CMP machines. Implementing a circuit to monitor cache utilization will bring significant hardware overhead. For an N-way associative cache of size C, the cache is divided into C/N sets. To estimate cache way utilization, one can profile cache utilization for full N ways, and derive the situation by assigning less cache way to the program based on LRU property. To record hit miss information at each cache position, a counter need to be attached. The UMON circuit simplifies this by only attaching a global counter to each cache position for all sets, and UMON-SS further simplifies this by only monitoring partial sets to represent a full cache set view. As [56, 103] point out, only less than 10% of the cache set needs to be sampled to have an accurate estimation of cache behavior. For the two programs co-run case, the scheduling problem can be solved by finding a cache way partition such that the summation of cache misses is minimized. The experiments use a simulator that assigns certain cache ways to different applications. Result show that partitions based on utilization are better than partitions based on demand.

Page coloring can be used to ensure continuous virtual memory can be evenly distributed across cache [101]. Later it is realized that this technique can also be used to enforce that an application only uses a subset of the cache space, which is a form of cache partitioning. Studies [21, 66, 95] demonstrate that performance, as well as fair utilization of cache resources in co-tenancy contention cases can be improved by applying this page color constraint. As applications running on a machine change over time, a dynamic re-coloring mechanism is needed. Zhang et al. [123] propose a hot-page based coloring mechanism such that only those frequently used pages are mapped with colors to guarantee good distribution across cache. As hardware page table entry has an access bit that can be set whenever a page is accessed, and page access can also be captured by page fault event, these features are employed for hot page identification.

As program phase transition can result in different cache utilization over time, a static coloring technique cannot capture this dynamic behavior, on the other hand, dynamic re-coloring involves allocating new page, page copying, and reclaiming old pages, which will introduce significant overhead. Intuitively, each application should be assigned a different color to provide isolation, but this may lead to low utilization. Therefore, assigning color based on an application's cache demand is more reasonable. Ye et al. [121] propose a page-coloring mechanism, COLORIS, which is embedded

into the Linux kernel similarly to [123] but use a new definition of hotness. Instead of traversing the page table to determine hot pages, they redefine hotness as the number of processes that share the same color. Colors are redistributed based on this demand by monitoring the cache miss rate of every process running on the machine. Initially, applications running on different cores are assigned to different groups of colors to enforce isolation, applications running on the same core share the same group of colors as they will run in an interleaved fashion, and thus there won't be contention between each other. During execution, the re-coloring engine emits a signal to expand the color assignment if process miss rate exceeds a threshold, or emits a signal to indicate an application can sacrifice subset of its cache partitions (color) if the cache miss rate below a threshold.

As cache partitioning is already supported by hardware, whether to partition or sharing the cache for a co-run group is discussed [13]. The scheduling problem is converted into a dynamic programing problem, such that, for a machine with cache size C and for each joining program  $p_i$ , the program is assigned with  $c_i$  cache that minimize the miss count of current program and the total miss count of an optimal partitioning for the first i-1 programs, whose allocated cache size is  $C - c_i$ . Suppose the scheduling of i programs with cache size k is  $S_{k,i}$  and mc is miss count, then the scheduling problem is equal to solving the DP problem below:

$$c_i = argmin\{mr(S_{C-c_i,i-1}) + mr_i(c_i)\}$$

$$S_{C,i} = S_{C-c_i,i-1} + c_i$$

The group miss ratio can be derived from individual footprints using the approach discussed in [115].

The above research focus on performance modeling or scheduling in a contention environment.

A sizable body of literatures focuses on identifying pathological portions in source code that will

result in contention and makes appropriate modifications to negate the effect.