### Michigan Technological University Digital Commons @ Michigan Tech

Dissertations, Master's Theses and Master's Reports

2019

# Contextual Bandit Modeling for Dynamic Runtime Control in **Computer Systems**

Jason Hiebel Michigan Technological University, jshiebel@mtu.edu

Copyright 2019 Jason Hiebel

### **Recommended Citation**

Hiebel, Jason, "Contextual Bandit Modeling for Dynamic Runtime Control in Computer Systems", Open Access Dissertation, Michigan Technological University, 2019. https://doi.org/10.37099/mtu.dc.etdr/942

Follow this and additional works at: https://digitalcommons.mtu.edu/etdr

### CONTEXTUAL BANDIT MODELING FOR DYNAMIC RUNTIME CONTROL IN COMPUTER SYSTEMS

Ву

Jason Hiebel

#### A Dissertation

Submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

In Computer Science

MICHIGAN TECHNOLOGICAL UNIVERSITY

2019

$\ensuremath{\mathbb{O}}$  2019 Jason Hiebel

This dissertation has been approved in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Computer Science.

Department of Computer Science

DISSERTATION CO-ADVISOR: Laura E. Brown

DISSERTATION CO-ADVISOR: Zhenlin Wang

${\bf Committee\ Member:}\ \textit{Nilufer\ Onder}$

Committee Member: Allan A. Struthers

Department Chair: Linda Ott

## To my mother,

a woman with a great capacity for tenacity and perseverance that I strive everyday to myself achieve

# Contents

| L | IST (       | of Figure | ES         |        |       |   | <br> | <br> | <br> |       |       | <br>• | <br>  | X    |

|---|-------------|-----------|------------|--------|-------|---|------|------|------|-------|-------|-------|-------|------|

| L | IST (       | OF TABLES | 8          |        |       |   | <br> | <br> | <br> |       |       |       | <br>  | XV   |

| Ρ | ${ m REFA}$ | .CE       |            |        |       |   | <br> | <br> | <br> |       |       |       | <br>Σ | KVI: |

| A | CKN         | OWLEGME   | NTS        |        |       |   | <br> | <br> | <br> |       |       | <br>٠ | <br>  | XIX  |

| A | BSTF        | RACT      |            |        |       |   | <br> | <br> | <br> | <br>• | <br>• | <br>٠ | <br>• | XX   |

| 1 | Int         | RODUCTIC  | )N         |        |       |   | <br> | <br> | <br> |       |       | <br>٠ | <br>  | 1    |

| 2 | Вас         | CKGROUNI  | )          |        |       |   | <br> | <br> | <br> |       |       | <br>٠ | <br>  | 7    |

|   | 2.1         | PERFORMA  | NCE MONI   | TORING |       |   | <br> | <br> | <br> |       |       |       | <br>  | 7    |

|   | 2.2         | Phase De  | TECTION .  |        |       |   | <br> | <br> | <br> |       |       |       | <br>  | 10   |

|   | 2.3         | MEMORY V  | √IRTUALIZA | TION . |       |   | <br> | <br> | <br> | <br>• | <br>• |       | <br>  | 12   |

|   | 2.4         | Hardware  | E MEMORY   | Prefe  | TCHIN | G | <br> | <br> | <br> |       | <br>٠ |       | <br>  | 13   |

|   | 2.5         | Multi-Ar  | med Band   | ITS    |       |   | <br> | <br> | <br> |       |       |       | <br>  | 16   |

### CONTENTS

|   |     | 2.5.1 Selection Strategies                 | 18 |

|---|-----|--------------------------------------------|----|

|   |     | 2.5.2 Contextual Bandits                   | 22 |

|   | 2.6 | Supervised Learning and Classification     | 24 |

|   | 2.7 | FEATURE SELECTION                          | 27 |

| 3 | Pac | GING MODE SELECTION                        | 31 |

|   | 3.1 | Introduction                               | 32 |

|   | 3.2 | BACKGROUND AND RELATED WORK                | 33 |

|   |     | 3.2.1 Memory Virtualization                | 33 |

|   |     | 3.2.2 Contextual Bandits                   | 35 |

|   | 3.3 | Dynamic Paging Mode Selection              | 37 |

|   |     | 3.3.1 Direct Sampling (DSP-SAMPLE)         | 38 |

|   |     | 3.3.2 Contextual Bandit Model (DSP-OFFSET) | 39 |

|   | 3.4 | EVALUATION                                 | 43 |

|   |     | 3.4.1 Experimental Environment             | 43 |

|   |     | 3.4.2 Experimental Design                  | 14 |

|   |     | 3.4.3 Results                              | 46 |

|   |     | 3.4.4 Profiling Cost                       | 49 |

|   | 3.5 | DISCUSSION AND CONCLUSION                  | 50 |

### CONTENTS

| 4 | HA  | RDWA  | RE M    | EMORY   | PRE    | EFETO | CHER | . U | TILI | ZA | ГІС | N. | <br> | <br> | <br>• | <br>• | <br>. 53 |

|---|-----|-------|---------|---------|--------|-------|------|-----|------|----|-----|----|------|------|-------|-------|----------|

|   | 4.1 | Intro | ODUCTI( | ON      |        |       |      |     |      |    |     |    | <br> | <br> |       | <br>• | <br>. 54 |

|   | 4.2 | Васк  | GROUN   | D AND ] | Relat  | ED W  | ORK  | • • |      |    |     | •  |      | <br> |       | <br>• | <br>. 55 |

|   | 4.3 | Cont  | TEXTUA  | l Band  | ıt Fr  | AMEW  | ORK  |     |      |    |     |    | <br> | <br> | <br>٠ | <br>• | <br>. 56 |

|   |     | 4.3.1 | Actio   | ON SELI | ECTION | ٧     |      |     |      |    |     |    | <br> | <br> |       |       | <br>. 58 |

|   |     | 4.3.2 | Cont    | EXT SE  | LECTI  | ON .  |      | • • |      |    |     |    | <br> | <br> |       |       | <br>. 58 |

|   |     | 4.3.3 | REWA    | RD FUI  | NCTIO  | Ν     |      |     |      |    |     |    | <br> | <br> |       |       | <br>. 59 |

|   |     | 4.3.4 | Polic   | cy Con  | STRUC  | TION  |      |     |      |    |     |    | <br> | <br> |       |       | <br>. 63 |

|   | 4.4 | Метн  | HODOLC  | GY      |        |       |      |     |      |    |     |    | <br> | <br> | <br>• | <br>• | <br>. 64 |

|   |     | 4.4.1 | Worl    | KLOAD S | SELEC  | TION  |      |     |      |    |     |    | <br> | <br> |       |       | <br>. 64 |

|   |     | 4.4.2 | Worl    | KLOAD I | Execu  | JTION |      |     |      |    |     |    | <br> | <br> |       |       | <br>. 66 |

|   |     | 4.4.3 | Ехре    | RIMENT  | al De  | ESIGN |      |     |      |    |     |    | <br> | <br> |       |       | <br>. 67 |

|   | 4.5 | Resui | LTS     |         |        |       |      |     |      |    |     |    | <br> | <br> | <br>• |       | <br>. 68 |

|   | 4.6 | Discu | USSION  | and Co  | ONCLU  | SION  |      |     |      |    |     |    | <br> | <br> |       |       | <br>. 72 |

| 5 | Ры  | RFORM | MANCE   | EVEN    | IT SE  | LECT  | ΓΙΟΝ |     |      |    |     |    | <br> | <br> | <br>• | <br>• | <br>. 75 |

|   | 5.1 | Intro | ODUCTI( | ON      |        |       |      |     |      |    |     | •  | <br> | <br> |       |       | <br>. 75 |

|   | 5.2 | Dyna  | міс Н   | ARDWAF  | re Pri | EFETC | HER. | Con | ITRO | L. |     |    |      |      |       |       | <br>. 77 |

### CONTENTS

|    | 5.3   | CORRELATION-BASED FEATURE SELECTION       | 8 |

|----|-------|-------------------------------------------|---|

|    | 5.4   | METHODOLOGY                               | 9 |

|    |       | 5.4.1 Workload Design and Execution       | 0 |

|    |       | 5.4.2 Dynamic Hardware Prefetcher Control | 1 |

|    |       | 5.4.3 Event Selection                     | 3 |

|    | 5.5   | RESULTS                                   | 5 |

|    |       | 5.5.1 DPL Prefetcher                      | 5 |

|    |       | 5.5.2 DCU IP Prefetcher                   | 1 |

|    | 5.6   | RELATED WORK                              | 3 |

|    | 5.7   | DISCUSSION AND CONCLUSION                 | 4 |

| 3  | Coi   | NCLUSION                                  | 7 |

|    | 6.1   | Contributions                             | 8 |

|    | 6.2   | FUTURE WORK                               | 8 |

| Bi | IBLIC | OGRAPHY                                   | 1 |

| A  | Coi   | PYRIGHT PERMISSION119                     | 9 |

# LIST OF FIGURES

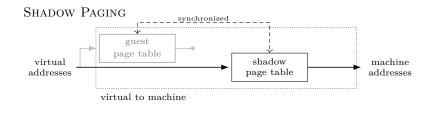

| 3.1 | A comparison of Shadow Paging and Hardware-Assisted Paging using       |    |

|-----|------------------------------------------------------------------------|----|

|     | EXTENDED/NESTED PAGE TABLES                                            | 34 |

| 3.2 | DESIGN AND PARAMETERS OF DSP-SAMPLE                                    | 38 |

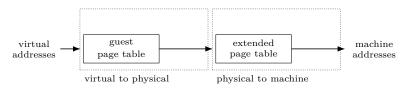

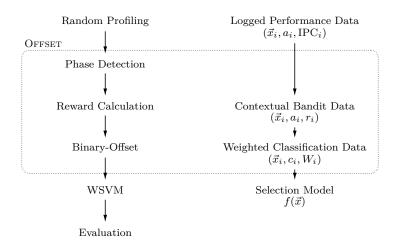

| 3.3 | OVERVIEW OF THE BINARY-OFFSET MODEL CONSTRUCTION AND BINARY-OFFSET     |    |

|     | MODEL EVALUATION WORKFLOWS FOR PAGING MODE SELECTION AND THE ASSOCI-   |    |

|     | ATED DATA TRANSFORMATIONS                                              | 39 |

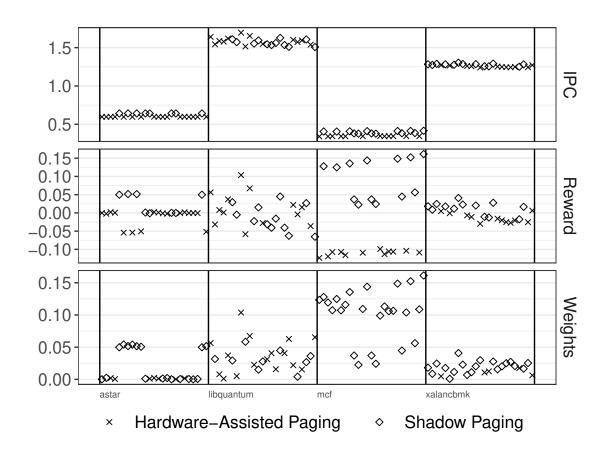

| 3.4 | IPC TO INSTANCE WEIGHT TRANSFORMATION: TOP; TRACES OF IPC AND PAGING   |    |

|     | MODE USING A RANDOM SELECTION POLICY FOR A SUBSET OF SELECT WORKLOADS. |    |

|     | MIDDLE; IPC TRANSFORMED TO REWARD. BOTTOM; BINARY-OFFSET TRANSFOR-     |    |

|     | MATION TO WEIGHTS                                                      | 42 |

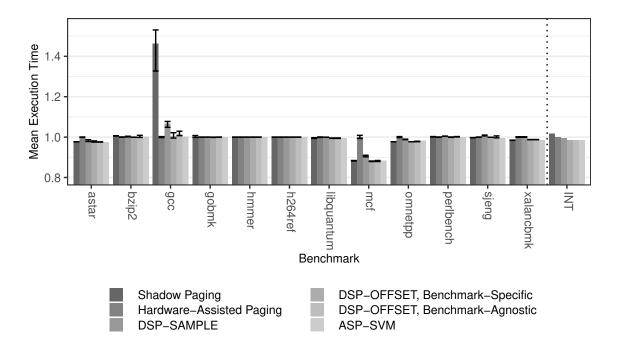

| 3.5 | MEAN NORMALIZED EXECUTION TIME FOR HARDWARE-ASSISTED PAGING, SHADOW    |    |

|     | PAGING, AND DYNAMIC SELECTIONS INCLUDING DSP-SAMPLE, DSP-OFFSET        |    |

|     | (BENCHMARK-SPECIFIC, BENCHMARK-AGNOSTIC), AND ASP-SVM [80] ON SPEC     |    |

|     | INT2006. Error bars indicate minimum and maximum normalized times      | 45 |

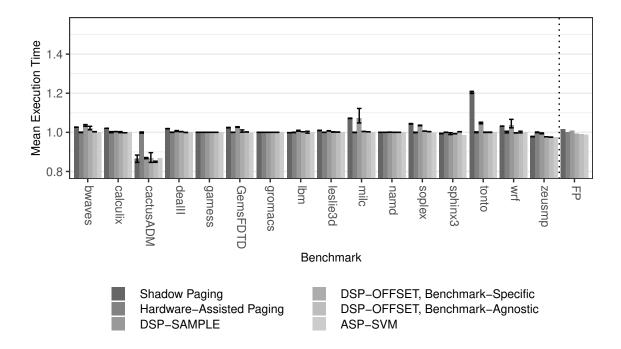

| 3.6 | Mean normalized execution time for Hardware-Assisted Paging, Shadow    |    |

|     | PAGING, AND DYNAMIC SELECTIONS INCLUDING DSP-SAMPLE, DSP-OFFSET        |    |

|     | (BENCHMARK-SPECIFIC, BENCHMARK-AGNOSTIC), AND ASP-SVM [80] ON SPEC     |    |

|     | FP2006. Error bars indicate minimum and maximum normalized times       | 46 |

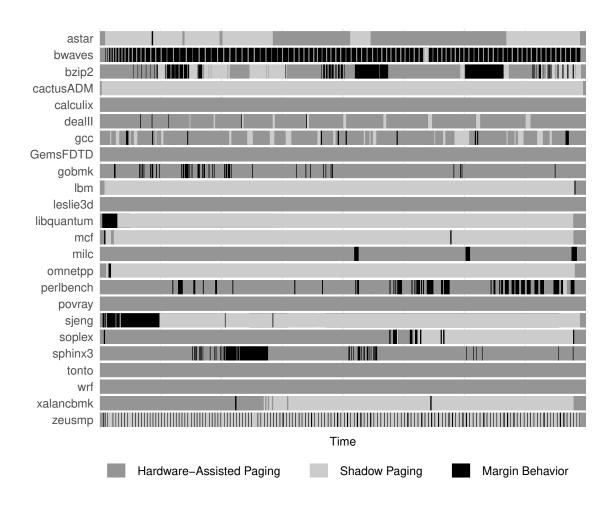

| 3.7 | PAGING MODES SELECTED OVER TIME FOR SPEC CPU06 BENCHMARKS USING THE    |    |

|     | BENCHMARK-AGNOSTIC DSP-OFFSET CONSTRUCTED ON SPEC INT06                | 48 |

### LIST OF FIGURES

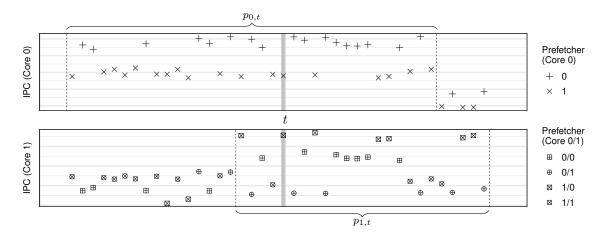

| 4.1 | A SMALL SAMPLE SEGMENT OF LOG DATA FROM A RANDOM EXECUTION OF A TWO-<br>CORE WORKLOAD                                                                                                        | 61 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

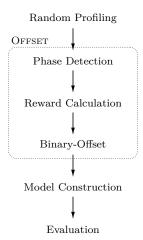

| 4.2 | OVERVIEW OF THE BINARY-OFFSET MODEL CONSTRUCTION AND MODEL EVALUATION WORKFLOW FOR HARDWARE MEMORY PREFETCHER UTILIZATION                                                                    | 62 |

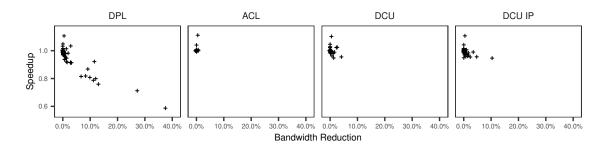

| 4.3 | CHANGE IN PREFETCHER PERFORMANCE AND MEMORY BANDWIDTH UTILIZATION FOR BENCHMARKS FROM SPEC CPU2006, SPEC CPU2017, AND PARSEC                                                                 | 65 |

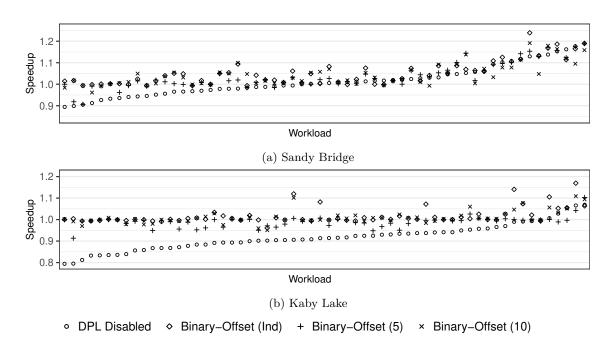

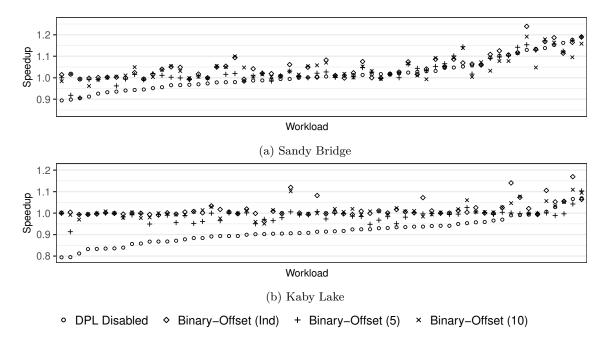

| 4.4 | Workload performance for DPL prefetcher related policies on Sandy Bridge and Kaby Lake experimental environments, relative to baseline All Enabled (all prefetchers enabled on all cores)    | 69 |

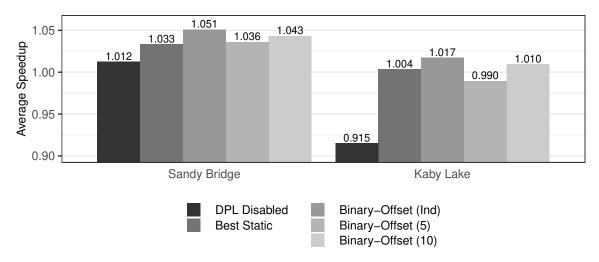

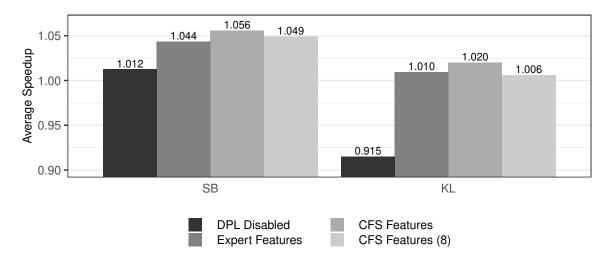

| 4.5 | Comparison of (geometric) mean policy performance on both the Sandy Bridge and Kaby Lake for the DPL prefetcher                                                                              | 69 |

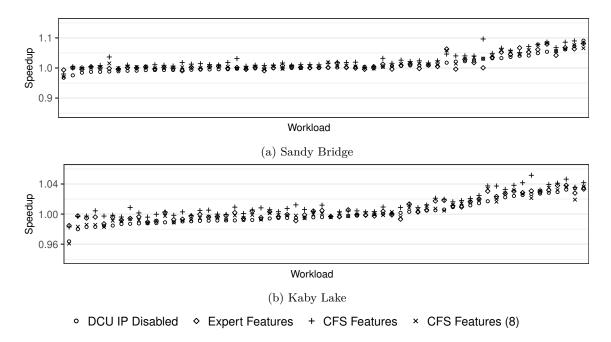

| 4.6 | WORKLOAD PERFORMANCE FOR DCU IP PREFETCHER RELATED POLICIES ON SANDY BRIDGE AND KABY LAKE EXPERIMENTAL ENVIRONMENTS, RELATIVE TO BASELINE ALL ENABLED (ALL PREFETCHERS ENABLED ON ALL CORES) | 71 |

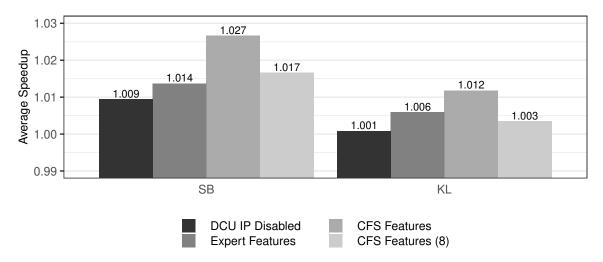

| 4.7 | Comparison of (geometric) mean policy performance on both the Sandy Bridge and Kaby Lake for the DCU IP prefetcher                                                                           | 71 |

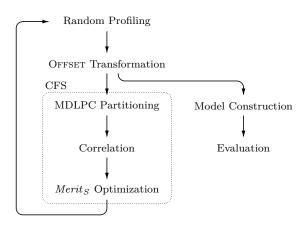

| 5.1 | OVERVIEW OF THE CFS PERFORMANCE EVENT SELECTION, BINARY-OFFSET MODEL CONSTRUCTION, AND BINARY-OFFSET MODEL EVALUATION WORKFLOWS FOR HARDWARE MEMORY PREFETCHER UTILIZATION.                  | 83 |

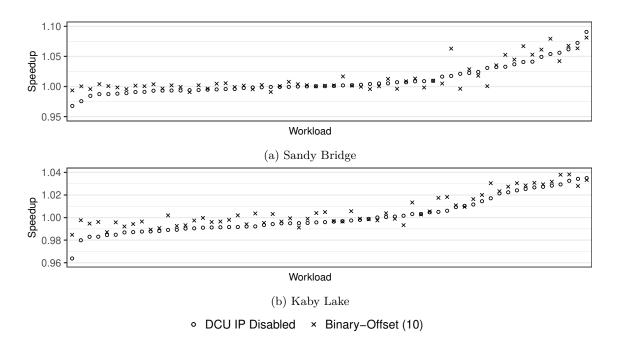

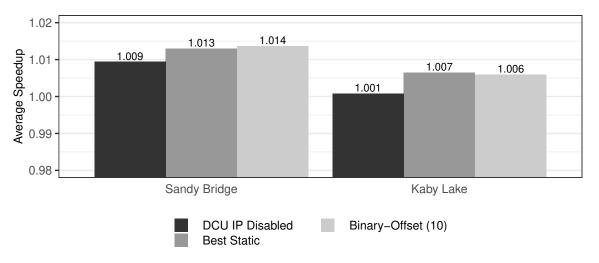

| 5.2 | Comparison of (geometric) mean policy performance on both the Sandy Bridge and Kaby Lake for the DPL prefetcher                                                                              | 87 |

| 5.3 | WORKLOAD PERFORMANCE FOR DPL PREFETCHER RELATED POLICIES ON SANDY BRIDGE AND KABY LAKE EXPERIMENTAL ENVIRONMENTS, RELATIVE TO THE BASE- LINE                                                 | 89 |

|     |                                                                                                                                                                                              |    |

### LIST OF FIGURES

| 5.4 | Comparison of (geometric) mean policy performance on both the Sandy |    |

|-----|---------------------------------------------------------------------|----|

|     | BRIDGE AND KABY LAKE FOR THE DCU IP PREFETCHER                      | 92 |

| 5.5 | Workload performance for DCU IP prefetcher related policies on      |    |

|     | SANDY BRIDGE AND KABY LAKE EXPERIMENTAL ENVIRONMENTS, RELATIVE TO   |    |

|     | THE BASELINE                                                        | 93 |

# LIST OF TABLES

| 3.1 | HARDWARE CONFIGURATION                                   | 43 |

|-----|----------------------------------------------------------|----|

| 4.1 | PERFORMANCE MONITORING EVENTS FOR CONTEXTUAL INFORMATION | 57 |

| 4.2 | HARDWARE CONFIGURATION                                   | 64 |

| 4.3 | BENCHMARK SELECTIONS BY SUITE                            | 66 |

| 5.1 | CFS EVENTS FOR SANDY BRIDGE DPL PREFETCHER               | 85 |

| 5.2 | CFS EVENTS FOR KABY LAKE DPL PREFETCHER                  | 86 |

| 5.3 | CFS EVENTS FOR SANDY BRIDGE DCU IP PREFETCHER            | 90 |

| 5 4 | CES EVENTS FOR KARY LAKE DCILIP PREFETCHER               | 91 |

# PREFACE

Chapter 3 contains material previously published in the Proceedings of the 47th International Conference on Parallel Processing (ICPP '18) [61]:

Jason Hiebel, Laura E. Brown, and Zhenlin Wang. Constructing dynamic policies for paging mode selection. In *Proceedings of the 47th International Conference on Parallel Processing*, ICPP '18, pages 72:1–72:9, 2018, doi:10.1145/3225058.3225082.

Chapter 4 contains material previously published in the Proceedings of the 48th International Conference on Parallel Processing (ICPP '19) [62]:

Jason Hiebel, Laura E. Brown, and Zhenlin Wang. Machine learning for fine-grained hardware prefetcher control. In *Proceedings of the 48th International Conference on Parallel Processing*, ICPP '19, pages 3:1–3:9, 2019, doi:10.1145/3337821.3337854.

The material described in Chapter 5 has been submitted for review and publication.

# ACKNOWLEDGEMENTS

I would first like to give my sincere appreciation and thanks to my advisors, Dr. Laura E. Brown and Dr. Zhenlin Wang, for their continued instruction and guidance. Through these past seven years, their counsel and enduring patience helped me learn, grow, and accomplish more than I imagined I could at the start of this journey. I would also like to recognize both Dr. Nilufer Önder and Dr. Allan A. Struthers. Their cheerful investment in my work was a fount of motivation to improve.

As the Turkish proverb goes, "always the trees that bear fruit are stoned." I'm glad that they saw potential in myself and my work and challenged me to succeed and excel.

Finally, I would like to extend my deepest gratitude to my mother, Mary Hiebel, father, Larry Clemo, and step-mother, Shannon Clemo, for their love and support. It was upon this bedrock that I was and continue to be able to build towards my future. From my first exposure to computer science in the shadow of my father, to the parallel struggles of working through graduate education with my mother, my family has been an indispensable source of comfort and inspiration.

## Abstract

Modern operating systems and microarchitectures provide a myriad of mechanisms for monitoring and affecting system operation and resource utilization at runtime. Dynamic runtime control of these mechanisms can tailor system operation to the characteristics and behavior of the current workload, resulting in improved performance. However, developing effective models for system control can be challenging. Existing methods often require extensive manual effort, computation time, and domain knowledge to identify relevant low-level performance metrics, relate low-level performance metrics and high-level control decisions to workload performance, and to evaluate the resulting control models.

This dissertation develops a general framework, based on the contextual bandit, for describing and learning effective models for runtime system control. Random profiling is used to characterize the relationship between workload behavior, system configuration, and performance. The framework is evaluated in the context of two applications of progressive complexity; first, the selection of paging modes (Shadow Paging, Hardware-Assisted Page) in the Xen virtual machine memory manager; second, the utilization of hardware memory prefetching for multi-core, multi-tenant workloads with cross-core contention for shared memory resources, such as the last-level cache and memory bandwidth. The resulting models for both applications are competitive in comparison to existing runtime control approaches. For paging mode selection, the resulting model provides equivalent performance to the state of the art while substantially reducing the computation requirements of profiling. For hardware memory prefetcher utilization, the resulting models are the first to provide dynamic control for hardware prefetchers using workload statistics. Finally, a correlation-based feature selection method is evaluated for identifying relevant low-level performance metrics related to hardware memory prefetching.

# Introduction

Modern operating systems and microarchitectures rely on a vast set of algorithmic choices, parameterizations, and heuristic models to facilitate performant resource allocation and program execution. Design decisions often offer a trade-off, improving the performance of some workloads while impairing the performance of others. When these design decisions and parameterizations can be affected at runtime, the system can be tuned or reconfigured to operate in a manner advantageous to the performance of the currently executing workload.

The opportunity for runtime control and configuration is ripe. Since the Nehalem microarchitecture (2008–), Intel has publicly exposed a set of four hardware memory prefetchers which can be enabled or disabled at runtime on each core [132, 67]. IBM POWER7 and later POWER microarchitectures (2010–) expose a highly configurable engine for hardware memory prefetcher control which further offers opportunities to configure prefetcher depth and stride [121]. Intel's Resource Director Technology is an emerging toolkit for hardware monitoring and resource allocation, available for the Xeon microarchitecture, which further expands the available system control mechanisms to include the ability to partition and assign cache ways to specific programs or threads (Cache Allocation Technology) and measure and throttle memory bandwidth usage per-core (Memory Bandwidth Monitoring, Memory Bandwidth Allocation). Effective utilization of these tools is an active body of research [70, 62, 69, 140, 100, 141, 142]. Additionally, there are many bespoke and application-specific examples of system control available in the computer systems literature, including paging mode utilization in virtual machine memory managers [15, 136, 80, 61], thread and data-center scheduling [120, 131, 41], power consumption control [38, 120], and feedback-directed optimization in virtual machines [7, 110, 32, 34, 109].

#### CHAPTER 1. INTRODUCTION

In *static* runtime control utilizes a fixed configuration for the duration of a workload's execution. In contrast, *dynamic* runtime control makes use of fine-grained profiling to affect system operation and adapt system capabilities in favor of the current system and workload characteristics. Developing effective models for dynamic runtime control can be challenging due to limited feedback. Performance measurements obtained through profiling only provide partial information, limited to the system configuration under which the profiling occurred. Feedback for alternative configurations can not be measured simultaneously with the same execution. One common method for providing comparative profiling relies on identifying representative regions of program execution or developing micro-benchmarks which are representative of certain types of workload behavior. Enumerative profiling of representative regions for the full set of available configurations provides full-information feedback, which is directly comparable within that region.

Determining which profiling metrics which are relevant to a runtime control decision presents a similar challenge of limited feedback. The Performance Monitoring Unit (PMU) [66, 6], available on most modern architectures, is a ubiquitous mechanism for measuring and characterizing system and workload behavior [52, 18, 146, 83]. The PMU exposes a large number of architecture events which can be measured at runtime using a small set of performance counters. Modern microarchitectures expose thousands of unique events but only provide up to eight performance counter registers with which to measure those events. There is significant pressure for these performance counter registers, as the number of performance events has far out-paced the number of events which can be measured simultaneously [149]. This is further complicated by the nature of those performance events. Which events are exposed by a particular system varies substantially both between vendors and between microarchitectures of the same vendor. Statistical sampling can allow for larger sets of performance events to be sampled at the cost of measurement error [14]. However, even with statistical sampling, measuring the full suite of performance events is both impractical, due to the incurred measurement error, and unnecessary, as a substantial number of events will be irrelevant or redundant to the application.

Instead, a subset of relevant and representative performance events should be chosen to drive runtime control. However, selecting relevant and representative performance events is often a laborious process. Reasoning about the relationship between low-level performance events and the resulting effect on configuration performance is often challenging even for domain experts. Performance event documentation, when available, is often terse, vague, and in some cases incorrect. Many performance events describe components or behaviors which are specific to a microarchitecture, and there are few performance events which are standardized across microarchitectures. Even for performance events which are consistently available, the relationship between those events and performance will also depend on microarchitecture design and the interaction between components.

This dissertation presents a framework for the uniform modeling of fine-grained, dynamic runtime control problems which are informed by measurable statistics of microarchitecture and workload behavior. This framework provides a simple and direct method for constructing effective runtime control models while mitigating the time cost and domain expertise required to achieve that performance. More specifically, the framework models fine-grained, dynamic runtime control as a contextual bandit [12]—a mathematical model which describes sequential decision making with so-called bandit feedback, which is representative of the limited feedback produced when profiling performance due to a control decision. At each iteration, the bandit observes some contextual information (workload behavior, according to performance event measurements), and uses that context, as well as existing domain knowledge about the control mechanism, to select an action (system configuration). In response, the bandit receives a reward (performance) dependent on both the context and selected action. By exploiting established off-policy contextual bandit methods (e.g., Binary-Offset [21]), profiling data that is obtained from random system control can adequately and efficiently capture the relationships between workload behavior, system configuration, and performance.

This work focuses on two motivating applications. The first application, paging mode selection, considers the trade-off in performance between common virtual memory abstractions (Shadow Paging, Hardware-Assisted Paging) in the Xen [16] virtual machine memory manager. The performance of each paging mode will favor certain types of memory access patterns. Shadow Paging introduces additional overhead to page table activity, which will, in turn, adversely affect the performance of workloads with larger memory working sets. Conversely, Hardware-Assisted Paging introduces additional overhead to the translation-lookaside buffer, which will, in turn, adversely affect the

#### CHAPTER 1. INTRODUCTION

performance of memory-intensive workloads. The second application, hardware memory prefetcher utilization, considers the configuration of existing hardware prefetchers. Prefetching is an effective tool for mitigating the cost of accessing DRAM. Future memory accesses are predicted and requested in advance of their potential use, ensuring that the requested memory is cached or in-flight by the time the memory is required. While prefetching is overwhelmingly effective for single core workloads, the added memory utilization due to prefetching can increase pressure for memory resources, such as the last-level cache and memory bandwidth, which are shared by multiple cores. This contention can be destructive to system-wide performance on multi-core systems. These two applications represent a scaffold in difficulty and complexity. In paging mode selection, there is a binary choice between paging modes, directed by the behavior of specific memory components (page table, translationlookaside buffer) behavior. In hardware memory prefetcher utilization, there is a combinatorial set of binary choices, selecting to enable or disable each of the four prefetchers on each core. Performance is not dictated by a single decision for a single core, but rather by the interaction of multiple decision, across multiple cores, through the shared last-level cache and memory bandwidth. This is further complicated by the complex interactions between cache and memory components which result in system-wide performance. Identifying which performance events are relevant and effective for dynamic prefetcher control presents a distinct challenge.

The main contributions of this work are three-fold. First, a mapping between dynamic runtime control and off-policy contextual bandits is developed. Leveraging the Binary-Offset algorithm [21], dynamic runtime control models are learned from profiling data acquired by utilizing random runtime control decisions over time. Second, the framework is evaluated for the two motivating applications, paging mode selection and hardware memory prefetcher utilization, with the scaffolded difficulty introducing additional modeling features. Third, a correlation-based feature selection method is described for selecting relevant performance events from the logged random profiling data, and is evaluated for hardware memory prefetcher utilization. The selected performance events are further analyzed in the context of available documentation to show that the events are substantiated by domain expertise.

The remainder of this work is organized as follows. Chapter 2 presents background material and

#### CHAPTER 1. INTRODUCTION

related work relevant to the system configuration and resource allocation, the contextual bandit, machine learning, and feature selection. Chapter 3 introduces the contextual bandit framework for runtime control, and details the application of this framework to the dynamic selection of performant paging modes in the Xen virtual machine monitor (Hiebel et al. [61]). Chapter 4 further details the application of the framework to the dynamic utilization of hardware memory prefetchers in multitenant workloads which suffer from contention for shared memory resources (Hiebel et al. [62]). Chapter 5 presents correlation-based feature selection for selecting performance events relevant to the hardware memory prefetcher utilization. Finally, Chapter 6 summarizes this work and describes several avenues for future work.

## BACKGROUND

### 2.1 Performance Monitoring

The Performance Monitoring Unit (PMU) is a commonly available component which allows for microarchitecture event occurrences to be measured at runtime with hardware assistance [66, 6]. The PMU consists of a small number (4-8) of configurable performance counters per CPU. Each performance counter is implemented as a pair of Model Specific Registers (MSRs), with one MSR for measurement and one MSR for configuration. Each counter is configured to observe an event through a two byte identifier: the first byte identifies the event, and the second byte identifies a mask. The event value identifies a distinct, high level event that can take place within the architecture, e.g., branch instructions retired (Intel event 0xC4, mnemonic BR\_INST\_RETIRED), and the mask specifies some subset of that behavior, e.g., near call branches that are taken (mask 0x20, mnemonic BR\_INST\_RETIRED: NEAR\_TAKEN). When enabled, the processor will increment the performance counter whenever the configured event occurs. Additionally, the PMU offers a small collection of fixed-function performance counters which measure specific events on each core, including instructions that retire execution (INST\_RETIRED.ANY) and core cycles while the processor core is not in a halt state (CPU\_CLK\_UNHALTED.THREAD, CPU\_CLK\_UNHALTED.CORE). The fixed-function and programmable counters operate independently of one another, freeing the user of using programmable counters to measure instruction throughput (measured as Instructions per Cycle, or IPC).

In addition to measuring event counts directly, the PMU can also be used to facilitate instructionlevel profiling. In event-based sampling, a counter is configured to trigger an interrupt after a fixed number of occurrences for a specified event. When that interrupt occurs, the performance

#### CHAPTER 2. BACKGROUND

monitor interrupt service routine will then record the PMU and processor state, including the current instruction counter, to a buffer. The result is a sub-sample of instruction pointer values where the sampling interrupt was triggered, which can, in turn, be used to identify code segments which frequently trigger the event of interest. Practically, event-based sampling is accomplished by setting the performance counter of interest to the maximum value, less the desired number of occurrences. When the counter overflows, the PMU will trigger an overflow interrupt which can be used to record the system state. Due to out-of-order execution and interrupt delays, the reported processor state can suffer from "skid": the reported state is several instructions offset from the instruction that triggered the interrupt. Intel's Precise Event-Based Sampling (PEBS) [66] and AMD's Instruction-Based Sampling (IBS) [6] provide low-latency event-based sampling directly in hardware, reducing the frequency of hardware interrupts for collecting sampling results and allowing for a more rich collection of processor state to be recorded (including branch status, data cache status, and load latency). Both PEBS and IBS minimize and bound the potential skid in program state.

Over time, the number of exposed performance events has grown substantially, exceeding a thousand available events on some recent Intel microarchitectures, while the number of performance counters has remained consistent [14, 42, 149]. As a result, only a small number of performance events can be sampled at any given time. Some performance events are limited to specific counter subsets. In many cases, high-level metrics require the measurement of multiple events to calculate. Ratios of events, such as the miss rate of a cache, are a common example which would require at least two events to calculate. The result is an increased demand for the (already scarce) set of programmable counters. Statistical sampling using time-based multiplexing is a common method for providing a larger set of logical performance counters by measuring subsets of performance events on the physical counters in shorter time slices [14]. However, multiplexing will omit some sampling error depending on the number of performance events measured and the sampling period size. Even with multiplexing, it is untenable to measure the full set of performance events simultaneously due to the resulting error. Alternatively, multiple sets of performance events can be sampled over several program executions, and the resulting traces can be merged. However, this is time-consuming of offline analysis and ill-suited for online analysis. Asynchronous events, such as interrupts and I/O events, can cause significant time drifts between individual runs, which, in-turn, complicates the process of merging offline traces.

Selecting meaningful performance events can itself be a challenge. The set of available events varies substantially between vendors, and even between microarchitectures from the same vendor. Performance events may also describe the behavior of components or operations that are specific to a microarchitecture, and there are few events which are standardized across microarchitectures. Often, there are complex interactions between architectural components which can obscure the meaning of performance events. This is further complicated by poor, and in some cases incorrect, documentation. The terse event descriptions that are published are often difficult to dissect. Without ample documentation (which is often unavailable), it can be challenging, even for a domain expert, to understand the translate the meaning of low-level performance measurements to a high-level impact on application and system behavior [96, 14, 40, 95, 143].

Nevertheless, the PMU is a popular tool for modeling and characterizing runtime system behavior, and affecting system behavior at runtime. A large number of commercial and open source software tools and APIs provide standardized cross-architecture interfaces for managing and operating the PMU. Popular examples include Intel vTune [91], PAPI [27], Perfsuite [82], and Perfmon2 [47]. For high-performance and parallel computing, specialized software suites, such as HPCTOOLKIT [2], PerfExpert [31], and Periscope [53], address scalable performance measurement and analysis for parallel systems and workloads.

Models for runtime modeling and prediction of performance [102, 18, 139, 49, 83] and energy consumption [72, 68, 38, 120, 19, 97, 56, 139] are plentiful, and target a breadth of architectural targets, runtime environments, and workloads. Methods such as Bubble-Up [92, 81] and ADP [146] characterize high-level performance descriptions by using low-level performance data obtained from the PMU. These models assist in translating low-level performance data into high-level, user understanaable descriptions of program behavior. These descriptions can, in-turn, be used to affect system configuration or program implementation in order to optimize performance or reduce energy consumption. In addition to providing insight into the performance characteristics of software, the ability to control the PMU at runtime allows software to self-assess performance and self-tune operation. Runtime control, directed by performance measurement, is a common usage of the PMU

#### CHAPTER 2. BACKGROUND

with applications spanning hardware memory prefetcher control [70, 62], efficient bandwidth allocation [69, 141], cache partitioning [140, 100, 142], paging mode utilization in virtual machine memory managers [15, 136, 80, 61], thread and data-center scheduling [120, 131, 41], and power consumption control [38, 120].

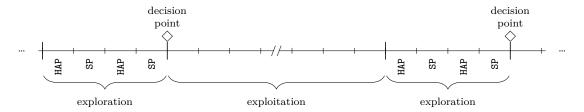

### 2.2 Phase Detection

A program will experience phases—periods of execution in which hardware metrics, including cache misses, branch mispredictions, energy consumption, and instruction throughput, are relatively stable. A phase change is an instance in a program's execution in which the behavior of a program undergoes a significant and noticeable change. For example, a program may be I/O-bound during one period of its execution, and once data has been serialized into memory, the program may become cpu-bound in a subsequent phase. Program phases can be observed at multiple granularities, with metrics showing stability over periods of tens of millions to tens of billions of instructions. Further, changes in phase typically occur across several hardware metrics simultaneously, suggesting that the characteristic behavior of the program is changing at those times. Phases can, and often will, reoccur multiple times during a program's execution [118]. Sherwood and Calder [114] illustrate that all but one benchmark program from SPEC CPU95 [124] either exhibited constant behavior for a majority of execution, or exhibited a cyclic, repeatable pattern of phases during that time.

Dhodapkar and Smith [43] identify phase changes by detecting changes in the instruction working set (segments of utilized memory regions) between multiple periods of execution. Basic Block Distribution Analysis (BBDA) (BBDA) [116, 117, 119] estimates the frequency in which each basic block is executed during a period. The result is a Basic Block Vector (BBV) describing a fingerprint of basic block utilization. By comparing the vector difference between BBVs in sequence over time, discovering phase changes amounts to a signal processing problem. Further, BBVs can be clustered in to identify repeated phase behavior. In addition to offline analysis and discovery, phase detection can also be performed online [98].

Alternatively, phase detection can be formulated as change-point detection applied to a signal of

performance characteristic sampling, such as IPC measurements at fixed intervals. A change-point is a time at which the statistical properties of a signal change. The segments between change-points will consist of stable periods of homogenous measurements corresponding to phase-like behavior. While change-point detection can broadly identify phases as periods of stable performance characteristics, further analysis would be required to identify periods corresponding to repeating or cyclic phase behaviors.

Consider a sequence of performance measurements  $(y_{0:n}) = y_0, \ldots, y_{n-1}$  and a sequence of ordered indices  $\tau_0, \tau_1, \ldots, \tau_{m-1}$  ( $\tau_0 = 0$  and  $\tau_{m-1} = n$ ). A common approach to change-point detection is to determine the indices  $\tau_{0:m}$  which, when segmenting  $(y_{0:n})$ , minimize the penalized cost

$$\left[\sum_{i=1}^{m-1} C(y_{\tau_{i-1}:\tau_i})\right] + f_{\beta}(m) \tag{2.1}$$

where C is the cost function for a segment (statistical critera), and  $f_{\beta}(m)$  is a penalty to guard against overfitting [78]. The cost function describes the statistical properties of a segment determined by two change-points. The more probable that the distribution of the segment changed at some internal point, the most costly the segment should be weighted. Common examples of cost functions include the negative log-likelihood [64], cumulative sum of squares [65], and quadratic loss. The penalty is typically linear with respect to the number of change points,  $f_{\beta}(m) = \beta m$ . The relative weight of each change-point's penalty,  $\beta$ , determined by some information-theoretic criterion based on the number of parameters p which are introduced when a change-point is introduced: Akaike's Information Criterion (AIC) [5],  $\beta = 2p$ , Bayesian Information Criterion (BIC) [111],  $\beta = p \log n$ , Modified Bayesian Information Criterion (BIC) [150],  $\beta = \frac{3}{2} p \log n + \frac{1}{2n} \sum_{i=1}^{m-1} (\tau_i - \tau_{i-1})$ .

Binary Segmentation [112] is an approximate recursive method with repeatedly considers the single change-point form of Equation 2.1. Segment Neighborhood [13] and Pruned Exact Linear Time (PELT) [78] solve Equation 2.1 exactly using dynamic programming. Segment Neighborhood requires an upper limit on the maximum number of change-points, whereas PELT dynamically determines the number of change-points. With regards to phase detection, there is a reasonable expectation that for some programs the number of phase changes will depend on the execution time

#### CHAPTER 2. BACKGROUND

of the program. As such, PELT is well-suited to phase change detection.

### 2.3 Memory Virtualization

Virtualization technology is a key component for data center management which, by simulating the functionality of hardware, allows multiple operating systems and applications to operate concurrently on the same physical machine. A virtual machine (VM) is a software container which provides hardware emulation. A virtual machine manager (VMM), or hypervisor, such as Xen [16] or VMWare [133] manages a collection of independent VMs (guests) and facilitates the illusion of direct native hardware access to each. Shadow structures are used to replicate the primary structures used by the guest, such as the page table; however, the additional layer of abstraction will unavoidably introduce overhead compared to the performance of a native system. In fully virtualized systems, the guests run without modification and with no knowledge that the guest is executing on a VM. Privileged operations are "trapped" by the VMM, so that the VMM can gain control of the system and emulate the operation before returning control to the guest. In paravirtualized systems, the guests are modified to directly call VMM-specific code to facilitate operations that require hardware emulation.

The memory management unit (MMU) is responsible for translating the virtual address space made available to a process to the physical address space in the hardware. The virtual and physical address spaces are divided into pages: fixed-size ranges of addresses, commonly 4 KB. A page table manages the mapping between virtual pages and physical pages, and the MMU consults the page table in order to translate virtual addresses into physical addresses. Due to the cost of walking the page table structure to find the desired mapping, the MMU will cache recent translations using the translation lookaside buffer (TLB). With virtualization, the physical memory of the guest is itself a virtual address space. The VMM must virtualize the MMU and facilitate a translation from either the virtual or physical addresses of the guest into machine addresses for use on the hardware.

Both Shadow Paging (SP) and Hardware-Assisted Paging (HAP) are common memory virtualization techniques for fully virtualized systems. Both techniques utilize an additional paging structure in the VMM which manages the mapping of guest addresses (virtual or physical) to machine addresses. The performance of either paging mode is dependent on workload, as both are subject to different types of overhead costs [24, 54, 1, 136].

In Shadow Paging, the VMMM maintains a shadow page table in parallel with the page table maintained by the guest. The shadow page table maps virtual addresses in the guest directly to machine addresses, bypassing the virtual to physical translation of the guest entirely. The shadow page table maps virtual addresses in the guest directly to machine addresses, bypassing the virtual to physical address translation of the guest all together. The shadow page table supersedes the guest page table, and the VMM installs the shadow page table. As updates to the guest's page table must be reflected in the shadow page table, expensive VM exits are required to maintain page table synchronization. This in turn increases the overhead of page table activity. This will have a significant, negative impact on workloads which suffer from a large number of page faults.

In Hardware-Assisted Paging, the VMMM maintains an extended page table (EPT) [54] or nested page table (NPT) [23] in sequence with the guest page table. Hardware support in the MMU performs the sequential mapping, first by translating virtual addresses into physical addresses using the guest page table, and then translating the physical addresses into machine addresses using the the extended/nested paging table. Unlike SP, page table updates do not require synchronization and expensive VM exits; however, the two-layer paging structure increases the cost of page table walks which, in turn, increases TLB miss latency. This will have a significant, negative impact on workloads with poor locality and a large working set (which exceeds the size of the TLB), as cached mappings will be evicted from the TLB before they are reused.

### 2.4 Hardware Memory Prefetching

Hardware memory prefetching is an effective technique for mitigating memory access latency. By observing and exploiting patterns in a program's memory accesses at runtime, a hardware prefetcher can generate memory requests ahead of the true request so that the desired memory is available (in the cache) or in-flight when demanded by the program. Hardware prefetching effectiveness

is determined by the coverage (proportion of misses that are eliminated because of prefetching), accuracy (proportion of prefetch targets which resulted in a hit), and timeliness (the latency between a prefetch targets availability vs reference) of the predicted prefetch targets. Inaccurate and untimely prefetching can place undue stress on memory resources, increasing memory bandwidth utilization and polluting the cache unnecessarily. It is also possible that untimely prefetch targets may be evicted from the cache before their use, prompting the memory to be fetched an additional time. Hardware prefetchers can struggle to obtain coverage in the presence of short streams, where the prefetcher does not have the opportunity to detect the direction and distance of the stream or stride, or when memory is accessed in irregular patterns [87]. While prefetchers are often effective in predicting memory accesses in a single-threaded setting, the increased utilization of, and contention for, shared memory resources such as memory bandwidth and the last-level cache can be destructive to multi-core performance [77, 93].

Prefetcher aggressiveness prevents a tradeoff in coverage, accuracy, timeliness, and resource utilization. An aggressive prefetcher will attempt to work well ahead of a detected memory access stream, relying on speculation in order to hide as much access latency as possible. The result is a likely increase in coverage and timeliness, at the expense of lower accuracy and an increase in memory bandwidth utilization and cache pollution due to the traffic and cache allocation of the incorrectly predicted prefetch targets. In contrast, a conservative prefetcher will attempt to operate with less speculation and more directly in response to current memory accesses. The result is a likely increase in accuracy, without the added cost of increased memory bandwidth utilization and cache pollution, but at the expense of lower coverage and worse timeliness.

Broadly, hardware prefetchers exploit both spatial and temporal locality in order to determine prefetch targets [94]. Stream prefetchers detect fixed-stride access patterns and on a cache miss will fetch one or more subsequent blocks along that stride, under the assumption that those cache lines will likely contain targets of future memory requests [73, 103, 35]. Correlation-based and Markov prefetchers [71, 115, 123] predict targets that may be the result of complex array accesses or pointer-chasing, allowing for a greater coverage on a broader set of memory access patterns. Prefetcher aggressiveness can be dynamically directed in hardware using feedback regarding the

accuracy, lateness, and cache pollution due to hardware prefetching [39, 123, 36, 106].

Since Nehalem (2008–), Intel microarchitectures have come equipped with four configurable prefetchers which can be enabled or disabled at runtime [132, 67]. Each prefetcher is configured independently of one another, and independently on each core, using the first four bits of each core's Model Specific Register (MSR) 0x1A4, with 0 indicating the at the corresponding prefetcher should be enabled, and 1 indicating that it should be disabled. By default, all four hardware prefetchers are enabled across all cores. The first pair of prefetchers, the Data Prefetch Logic (DPL) and Adjacent Cache Line (ACL) prefetchers, operate on the L2 cache. The DPL is a stream prefetcher which is capable of detecting both ascending and descending sequences of accesses issued from the L1 cache within 4 K page boundaries. The prefetcher is capable of detecting and maintaining up to 32 data access streams, with up to one forward and one backward stream per page. Recent microarchitectures have refined the operation of the prefetcher in order to better address memory contention concerns: when there are few outstanding memory requests, the DPL will operate up to 20 lines ahead of the most recent load request in the stream; when there are many outstanding memory requests, the DPL will operate in a more restricted fashion and will only cache the prefetched memory in the last-level cache. The ACL is a spatial prefetcher which fetches adjacent cache lines which form a 128-byte aligned pair. While more restrictive than the DPL, the ACL prefetcher does not require a detected access stream to operate. The second pair of prefetchers, the Data Cache Unit (DCU) and Instruction Pointer (DCU IP) prefetchers, operate on the L1 cache. The DCU is an ascending stream prefetcher which reacts to ascending accesses in recently loaded data. The accesses are assumed to be part of access stream and the immediately following line is prefetchers. The DCU IP is an ascending/descending stride prefetcher which operates on half page (2 K) limits. Both prefetchers are only triggered under a restricted set of conditions, including a low load miss rate and the lack of a memory barrier in the pipeline.

Since POWER7 (2011–), IBM POWER microarchitectures have come equipped with a highly configurable hardware prefetching engine for an L1 stream prefetcher [121, 122, 58, 70]. The stream prefetcher is capable of detecting and exploiting up to 16 independent data streams resulting from memory requests in the L1 cache. Prefetching can be configured to enable or disable the detection

of load and store streams, and can independently be configured to enable or disable the detection of streams with non-unit strides. In addition, the depth of the stream buffer can be specified as one of six broad categories, from "shallowest" to "deepest". By default, load streams are enabled, both store streams and non-unit stride streams are disabled, and the prefetcher depth is set to "deep" (below "deeper" and "deepest"). Recent improvements in the POWER7+ and POWER8 microarchitectures have included configuration for prefetcher urgency to direct how aggressively the prefetcher will operate to attain the specified depth when a stream is detected.

# 2.5 Multi-Armed Bandits

First developed in Robbins [107], the multi-armed bandit [107, 55, 33, 28] describes a sequential decision process with limited feedback. The bandit selects some actions (or arms) to play in sequence, and in response to each action the bandit receives a (potentially stochastic) reward for that action. The rewards for the remaining actions are unobserved (so called "bandit feedback"). The goal of the multi-armed bandit is to select actions which will maximize the cumulative reward received. To start, the bandit has no knowledge of how rewarding each action will be, and must balance exploration (selecting actions to model the rewards of each action) and exploitation (selecting actions which are strongly believed to be optimal). The origin of the term multi-armed bandit comes from the slang "one-armed bandit", describing an old-style slot machine operated by pulling a long handle at the side.

Clinical trials are a historical motivation for the multi-armed bandit. In a clinical trial, each patient can be assigned only one treatment (action), and only the result of that treatment can be measured for a particular patient (bandit feedback). There are two conflicting goals involved in this process: first, to correctly identify the best treatment (requiring exploration), and second, to provide the best standard of care to the patients in the trial (requiring exploitation). As the trial continues, there is an obligation, especially in the case of a severe disease, to dynamically adjust treatment selection so that the selections favor more rewarding options. However, less rewarding treatments must still be utilized (with less frequency) to prevent the trial from greedily exploiting a suboptimal treatment

due to non-representative samples early on.

Formally, the multi-armed bandit problem is defined by a set of  $K \geq 2$  possible actions and sequences  $(X_a) = X_{a,1}, X_{a,2}, \ldots$  of rewards for each action a. At each time step  $t = 1, 2, \ldots$ , the bandit will select some action  $a_t$ , and will collect reward  $X_{a_t,t}$  in response. The behavior of a bandit is determined by the action selection strategy. The quality of a particular strategy is expressed in terms of the regret, or lost reward, accumulated by selecting suboptimal actions,

$$R_n = \max_{a} \left( \sum_{t}^{n} X_{a,t} \right) - \sum_{t}^{n} X_{a_t,t}$$

(2.2)

as the difference between the total reward of the best performed action (the optimal strategy) and the total reward obtained by by the bandit over n selections. In practice, this from of regret is not practical to estimate, as the reward may be chosen according to some stochastic or adversarial process. Instead, the *pseudo-regret*,

$$\overline{R}_n = \max_a \mathbb{E}\left[\sum_{t=1}^n X_{a,t} - \sum_{t=1}^n X_{a_t,t}\right]$$

(2.3)

measures the regret compared to the action which has the optimal expected reward, as opposed to measuring the regret over the selected rewards rewards. The goal is to determine a strategy which minimizes the potential regret of the bandit.

The structure of the rewards will strongly influence action selection strategy. Rewards can be drawn stochastically or adversarially. In the stochastic bandit case, the rewards for each arm,  $(X_a)$ , are independent and identically distributed (i.i.d.) according to some distribution  $\nu_a$ . In the adversarial (non-stochastic) bandit case, the rewards are assumed to be generated by some adversary. The adversary is allowed to assign rewards with full knowledge of the bandit's selection process, but must make the reward assignments before the bandit selects and reveals its action (otherwise, the adversary could simply assign an arbitrary reward to the selected action). The adversarial setting illustrates the need for minimizing regret, as opposed to maximizing reward. If the adversary were simply attempting to minimize the bandit's accumulated reward, then it could simply set the poor rewards for every action. Instead, like in a rigged casino, the adversary attempts to maximize the

reward that the bandit could have accumulated with optimal selections.

Whereas the standard multi-armed bandit formulation considers an exploration-exploitation tradeoff, pure exploration bandits [29, 9, 30, 76] instead consider a distinct exploration phase which is

constrained to a fixed number of action selections. During the exploration phase, the bandit selects

actions and obtains bandit feedback in order to identify the optimal action with high confidence,

so that the recommended action can be exploited in the subsequent phase. Only the regret of the

recommended action is considered. An example application for pure exploration bandits, given in

Audibert and Bubeck [9], considers channel allocation in mobile networks. Before transmission, a

transmitter can first explore the set of (noisy) channels, for a brief period, to identify which channel

will be the best over which to communicate. Transmission is then performed over the channel that

the bandit believes to be the best.

#### 2.5.1 Selection Strategies

Action selection strategies are responsible for carrying out the exploration-exploitation balance of a bandit. Several actions election strategies appear commonly in the literature, introduced and modified to bound the regret of the bandit in some theoretical capacity. For the stochastic bandit, this includes strategies such as  $\epsilon$ -Greedy [129], upper confidence bounds [11], and Thompson Sampling [4]; for the adversarial bandit, the exponential-weight algorithm for exploitation and exploitation [12].

#### $\epsilon$ -Greedy

The  $\epsilon$ -Greedy approach balances exploration and exploitation at random. The bandit tracks the mean observed rewards for each action. Most of the time, the bandit selects the action with the greatest mean reward. Otherwise, with some small probability  $\epsilon$ , the bandit instead selects an action to take at random. For the stochastic multi-armed bandit, in the case of a fixed  $\epsilon$ , the regret of

$\epsilon$ -Greedy is grows linearly with respect to the horizon:

$$\overline{R}_n = \max_a \mathbb{E}\left[\sum_t^n X_{a,t} - \sum_t^n X_{a_t,t}\right]$$

$$= n \mu^* - \sum_t^n \mathbb{E}\left[\mu_{a_t}\right]$$

$$= n \mu^* - n \left[(1 - \epsilon) \mu^* + (\frac{\epsilon}{K}) \sum_a \mu_a\right]$$

$$= n \left(\frac{\epsilon}{K}\right) \sum_a (\mu^* - \mu_a)$$

(2.4)

where  $\mu_a$  are the mean rewards drawn from  $\nu_a$  and  $\mu^* = \max_a \mu_a$ . With careful annealing of the  $\epsilon$  value, by scaling  $\epsilon$  inversely proportional to time, the regret can instead be bounded logarithmically [11].

#### UPPER CONFIDENCE BOUNDS

Upper Confidence Bound (UCB) methods facilitate the exploration-exploitation tradeoff by selecting actions according to bounds on each action's reward which hold with high probability. The bandit tracks the mean observed rewards,  $\hat{X}_a$ , and the total number of plays,  $T_a$ , for each action. With each selection, the bandit strengthens the estimate of the selected action's mean reward. In response, the bound on the reward will shrink towards the estimate.

For the stochastic bandit, the reward observations for each action are *i.i.d.* random variables. When the rewards are further bounded to the unit interval [0, 1], the difference between the estimated and true mean reward of each action can be bounded probabilistically according to Hoeffding's inequality [63]:

$$P(\mu_a \ge \hat{X}_a + U_a) \le e^{-2T_a(U_a)^2},$$

(2.5)

where  $\mu_a$  are the mean rewards drawn from  $\nu_a$ , and  $U_a$  are upper bounds on the estimates for each action. The probability is bounded by some small  $p = e^{-2T_a(U_a)^2}$  such that it is unlikely the upper-bounded reward estimate exceeds the true reward. For any  $p \ll 1$ , the reward estimate falls

below the bound

$$\hat{X}_a + U_a = \hat{X}_a + \sqrt{-\log p/2 \, T_a}.\tag{2.6}$$

almost always. A similar bound can be found for sub-Gaussian distributions. If the observed rewards are not bounded, but instead are sub-Gaussian random variables with variance  $\sigma^2$ , then the difference between the estimated reward and the true reward can be bounded as

$$P(\mu_a \ge \hat{X}_a + U_a) \le e^{-t(U_a)^2/2\sigma^2},$$

(2.7)

which produces the upper-bound reward estimate

$$\hat{X}_a + U_a = \hat{X}_a + \sqrt{-2\sigma^2 \log p/T_a}.$$

(2.8)

UCB greedily selects the action a which maximizes the upper-bounded reward estimate  $\hat{X}_a + U_a$ . When selected, the upper-confidence estimate of the action will shrink, as the estimate of the sample mean is less likely to deviate from the true mean with the larger sample size. Actions with a smaller estimated reward will be selected on occasion, after the most rewarding action is selected sufficiently often to shrink the upper-bound estimate.

The UCB1 algorithm [11, 10] decreases the probability over time according to the schedule  $p = t^{-4}$ , which results in an upper confidence estimate of

$$\hat{X}_a + U_{a,t} = \hat{X}_a + \sqrt{2\log t/T_a}.$$

(2.9)

Note that the upper-bound estimate is very generous, given the loose assumptions for Hoeffding's Inequality (bounded on [0,1]). The pseudo-regret for UCB1 is bounded logarithmically:

$$\overline{R}_n \le 8 \sum_{a: \mu_a < \mu^*} \left[ \frac{\log n}{\mu^* - \mu_a} + \left( 1 + \frac{\pi^2}{3} \right) (\mu^* - \mu_a) \right]$$

(2.10)

The first term indicates that each action will be selected a logarithmic number of times with respect to the number of plays, and actions which are close to optimal will be selected more often. The second term indicates a small number of expected plays which are required to address unlikely cases.

The asymptotic behavior of the pseudo-regret for UCB1 is bounded sub-linearly:

$$\overline{R}_n \in \mathcal{O}(\sqrt{K \, n \log n}). \tag{2.11}$$

## THOMPSON SAMPLING

Thompson sampling is a probability matching technique which models the prior distribution of the mean rewards for each action. Actions are selected according to the corresponding posterior distributions—the bandit samples from each action's posterior distribution, and selects the action with the greatest sample mean. After the reward is observed, the prior distribution for the selected action is updated accordingly.

Consider a bandit with Bernoulli rewards,  $X_{a,i} \sim Bernoulli(\mu_a)$ . After a sequence of actions, the conjugate priors  $\mu_a \sim Beta(\alpha_a, \beta_a)$  describe the distribution of the sample mean for action a, where  $\alpha_a - 1$  denotes the number of successes (reward = 1) and  $\beta_a - 1$  describes the number of failures (reward = 0). To begin, before any actions have been selected, the priors for every action are initialized to Beta(1,1). This corresponds to the uniform case, where each value of the mean is equally likely. The Bernoulli bandit generates samples of the mean from each action's prior, and chooses the action with the largest sample. The prior of the selected action is then updated according to the reward,  $(\alpha_a, \beta_a) \leftarrow (\alpha_a + X_{a,t}, \beta_a + (1 - X_{a,t}))$ . The asymptotic behavior of the pseudo-regret for Thompson sampling for the Bernoulli bandit is bounded sub-linearly:

$$\overline{R}_n \in \mathcal{O}(\sqrt{K \, n \log n}). \tag{2.12}$$

#### EXPONENTIAL-WEIGHT ALGORITHM FOR EXPLORATION AND EXPLOITATION

In contrast to the previous selection strategies, the Exponential-Weight Algorithm for Exploration and Exploitation (EXP3) [12] considers action selection for the adversarial bandit with bounded rewards. Without loss, assume the actions are bounded to the interval [0,1]. Instead of measuring

regret in terms of the accumulated reward, the EXP3 strategy measures regret in terms of the accumulated loss,  $l_{a,t} = 1 - X_{a,t}$ , inflicted by the adversary for choosing an action a. The bandit incorporates randomness to the action selection strategy in order to subvert the adversarial selection of rewards. With randomness, a sub-linear regret bound is achievable. Without randomness, the adversary can perfectly emulate the selection strategy and maximize the loss for the predicted action.

The bandit tracks estimates of the cumulative loss for each action,  $\hat{L}_a$ . Actions are selected randomly with probability proportional to an exponential weighting of the cumulative loss estimate,

$$p_a \propto e^{-\eta_t \, \hat{L}_a},\tag{2.13}$$

where  $\eta_t$  is a non-increasing schedule of weights. Rather than use the losses imparted by the adversary directly, the bandit accumulates the unbiased estimation of the loss,  $\hat{l}_{a_t} = l_{a_t,t}/p_{a_t}$ . For the decreasing schedule  $\eta_t = \sqrt{\log K/t} K$ , the asymptotic behavior of the pseudo-regret for EXP3 can be bounded sub-linearly:

$$\overline{R}_n \in \mathcal{O}(\sqrt{n \, K \log K}). \tag{2.14}$$

# 2.5.2 Contextual Bandits

The contextual bandit [12, 22, 85, 89] (alternatively, the partial label problem [74], the associative bandit problem [127], bandits with side information [134, 135, 147], bandits with a concomitant variable [137], associative reinforcement learning [12]), extends the multi-armed bandit to include side-information in the decision procedure. Prior to selecting an action, the contextual bandit first perceives some information  $\vec{x}_t$  about the environment (a context) in which the action will occur. The resulting reward observed by the contextual bandit depends on both the action and the context.

A common application of the contextual bandit is the personalized selection of internet advertisement. Websites have a wealth of logs which detail historical usage: observable quantities about the user, such as the visiter's history, queries, and provided personal data (context), the advertisements served to the visiter (action), and whether or not the visiter clicked on the advertisement (Bernoulli reward). The goal is to maximize the click-through rate of advertisements by selecting advertisements which are appropriate to the visiter and thus rewarding to the website.

In order to manage the complexity introduced by the addition of contextual information, assumptions on the context space and reward are introduced. In the simplest case, when the contextual information specifies an element from a finite set of contexts, the contextual bandit can be interpreted as a set of independent, context-free bandits, indexed by the context [134, 135]. When the context is drawn from a vector space, a common constraint is to assume that the reward is linear [37, 3] or Lipshitz [89] in expectation. Regardless of the constraints, the selection strategies underpinning various solutions to the contextual bandit generally follow the selection strategies for the multi-armed bandit: greedy [85], upper confidence bound [37], Thompson sampling [3], and adversarial models [22].

Off-policy methods [86, 44] utilizes the partial-label results of a contextual bandit in order to construct an action selection strategy from logged data. Similarly to pure exploration bandits in the multi-armed case, exploration and exploitation are not interleaved; rather, exploration data is constructed from the exploration of a previous action selection strategy (as tuples of context, action, and reward), and the resulting log data is used to construct a selection strategy which is then exploited. The advantage of using log data is its ubiquity—many selection strategies can be evaluated against the logged exploration data without requiring in situ evaluation, which may be impractical and costly. In contrast to pure exploration bandits, the exploration procedure is not the focus. Due to the limitation of bandit feedback, log data is insufficient to directly simulate the result of some new selection strategy. One alternative is to estimate the contextual reward function directly using the available log data, and use the resulting regression model for simulating selection strategies. Another alternative is to utilize inverse propensity scoring (IPS) [108] to shift the proportion of actions between the log data and the selection's actions [86]. Combining both the direct and IPS methods addresses the deficiencies of each [44]. Instead of modeling the reward directly, the Offset-Tree [21] instead maps the logged partial label data to a weighted classification problem. The resulting weighted classification data is then amenable to a broad suite of machine learning techniques for feature selection, dimension reduction, and classification.

# 2.6 Supervised Learning and Classification

In machine learning, classification is the supervised learning task of categorizing new instances based on a training set of data containing observations (or instances) whose category membership is known. For example, determining a diagnosis for a patient given a set of diagnostic test results, categorizing emails as either spam or not spam given the contexts of the email, or labeling an image according to the object represented.

Consider a training set of labelled instances  $(\vec{x}_1, y_1), (\vec{x}_2, y_2), \dots, (\vec{x}_n, y_n)$ , each described by a vector  $\vec{x}_i$  of quantifiable features, and a label (class)  $y_i$  drawn from a finite set of categories. Each feature may be nominal, ordinal, or numerical. A nominal feature takes the form of a set of options which have no intrinsic ordering, e.g., sex,  $\{male, female\}$ , blood type,  $\{A, B, AB, O\}$ , or boolean-valued sets,  $\{true, false\}$  or  $\{spam, notspam\}$ . This is sometimes also referred to as a categorical feature. A ordinal feature takes the form of a set of options that have an intrinsic ordering, e.g., sizes,  $\{small, medium, large\}$ , or letter grades,  $\{F, D, C, B, A\}$ . Numerical features are drawn from (subsets of) some number space, e.g., integers,  $\mathbb{Z}$ , or real numbers,  $\mathbb{R}$ .

Classifiers attempt to select some function, or hypothesis,  $h(\vec{x})$  which categorizes instances by mapping the feature vector  $\vec{x}$  to a predicted category y. Ideally, the classifier attempts to maximize the accuracy of the classes predicted by the hypothesis when presented with novel (unlabeled) instances.

Deterministic (non-probabilistic) classifiers, such as the support vector machine, separate the feature space in to regions and associate each region with a class. When presented with a new instance, the classifier returns the class associated with the region containing the instance. Probabilistic classifiers, such as Logistic Regression and Naïve Bayes, instead generate a distribution describing the probability that the instance is a member of each class. The instance can then be labelled according to the class with the largest probability. Alternatively, the classifier can abstain from providing a class if there is insufficient confidence for any of the classes. The collection of classifier methods is rich and detailed, and can not be completely described here.

The Support Vector Machine (SVM) is a non-probabilistic, binary classifier which models the clas-

sification boundary separating instances of the training data, according to class, with the largest margin. Consider a binary classification problem with class labels  $\{+1, -1\}$  (positive and negative labels, respectively). In the hard-boundary case, where training data instances of each class are linearly separable, i.e., that there exists some linear hyperplane which separates the positive and negative instances, the support vector machine can be modeled by the constrained optimization problem

$$\underset{\vec{w},b}{\operatorname{arg min}} \quad \frac{1}{2} ||\vec{w}||^2$$

subject to  $y_i \ (\vec{w} \cdot \vec{x}_i - b) \ge 1$ ,

where  $\vec{w} \cdot \vec{x}_i - b \ge 1$  and  $\vec{w} \cdot \vec{x}_i - b \le 1$  represent the parallel linear functions comprising the margin and separating the positive and negative instances of the training data. The instances which fall directly on the margin, and thus constrain (or support) it, are referred to as support vectors. The margin can be completely determined by these support vectors.

More generally, when the training data instances are not linearly separable, a collection of slack variables can be added to allow for instances to violate the margin constraint at the expense of some error. The soft-margin SVM is be modeled by the constrained optimization problem

$$\underset{\vec{w}, b, \xi_{i}}{\operatorname{arg min}} \quad \frac{1}{2} ||\vec{w}||^{2} + C \sum_{i=1}^{n} \xi_{i}$$

subject to  $y_{i} (\vec{w} \cdot \vec{x} - b) \ge 1 - \xi_{i}$ ,

$$\xi_{i} \ge 0,$$

(2.16)

where  $\xi_1$ ,  $\xi_2$ , ...,  $\xi_n$  are slack variables, and C is a hyper-parameter representing the relative weight between the margin size and slack variable error. The slack variables represent a form of hinge-loss,  $\max(0, 1 - (y_i \ \vec{w} \cdot \vec{x}_I - b))$ . When the margin would lead to correctly classifying a training instance,  $\xi_i = 0$  and the instance contributes no additional loss to the optimization function. Otherwise, the instance accumulates loss linearly with regards to it's distance from the boundary.

As the soft-margin formulation satisfies the Karush-Kuhn-Tucker (KKT) conditions [], Equation 2.16 can be reformulated as the quadratic optimization problem (the so-called dual form),

$$\underset{c_i}{\operatorname{arg max}} \quad \sum_{i}^{n} c_i + \frac{1}{2} \sum_{i}^{n} \sum_{j}^{n} y_i c_i (\vec{x}_i \cdot \vec{x}_j) c_j y_j$$

subject to

$$\sum_{i}^{n} c_i y_i = 0,$$

$$c_i \ge 0,$$

$$c_i \le \frac{1}{2n\lambda},$$

(2.17)

where  $c_i$  are Lagrange multipliers (or Kuhn-Tucker coefficients) [90]. Quadratic programming solvers allow for the efficient optimization of Equation 2.17. When the margin would lead to correctly classifying a training instance ( $c_i = 0$ ), the instance contributes no additional loss to the optimization function. When  $0 < c_i <= \frac{1}{2n\lambda}$ , the training instance exists on or across the margin and the resulting instance is a support vector. The weight vector

$$\vec{w} = \sum_{i} c_i y_i \vec{x}_i \tag{2.18}$$

can be computed as a linear combination of the support vectors (as  $c_i = 0$  for any training instances that are not support vectors).

In some problems, training instances may not be of equal value. Prior knowledge might dictate that the quality of instances differ in a quantifiable manner, or that the relative importance of instances, and thus the weight those instances should impact on the classifier, can vary. In an instance-weighted classification problem, each training instance is accompanied by a positive weight value. That weight will scale the loss contributed by the corresponding instance. The meaning of that weight, and whether that weight is constrained to a given range, will depend on the problem. Instance weights can be directly incorporated into the formulation of a classification algorithm, by using weights as coefficients in the classification loss (e.g., for SVMs [145]). Alternatively, the instance weights can be used to sample instances from the training data set, resulting in higher weighted training instances being selected with a proportionally higher probability than lower weighted training instances. The resulting, unweighted training data set is then amenable to the full suite of classical, unweighted classification methods. Typically, a collection of training data set samples are taken, and the resulting

classifiers constructed for each set are combined in to an ensemble. The probability can be taken as the normalized weight values. Zadrozny et al. [148] instead proportion the selection of weight according to the maximum weight value.

Convex loss classifiers, such as Logistic Regression and SVMs, are popular due to the existence of efficient numerical solvers. However, these methods are sensitive to the presence of class label noise. The loss of mislabeled instances will increase with respect to the distance to the decision boundary (e.g. logarithmically, or linearly with hinge loss). The result is a learned decision boundary which is necessarily skewed towards the label outliers in order to minimize the loss of those outliers. Generally, convex loss functions act as surrogates to the 0-1 misclassification loss,  $\frac{1}{n}\mathbb{I}[h(\vec{x}_i) = y_i]$ . While robust to label outliers, optimizing the 0-1 misclassification loss directly is NP-Hard [17]. Label outliers can be addressed by either using a classifier which is robust to label noise, perhaps accepting a non-convex loss function which is less efficient to optimize, or filtering instances which appear to be mislabeled [51].

# 2.7 Feature Selection

Feature selection is a technique for identifying and removing features which are redundant or irrelevant to an outcome [79, 57]. Focusing the attention of a supervised learning to the subset of useful features has a number of advantages. Most notably, feature selection helps mitigate the effect of the curse of dimensionality: the amount of training data needed to learn grows exponentially with the number of features. There are also implications for training time, as fewer features reduces the set of parameters which must be learned, and for data exploration, as the prominent features can be more easily visualized and interpreted in a lower dimensional space. Feature selection methods can broadly be categorized as filter methods, wrapper methods, and embedded methods:

Filter methods are a computationally efficient class of feature selection algorithms which operate directly on the characteristics of the training data set, relating features to the corresponding classes. As such, they can be thought of as a preprocessing step, first identifying the relevant features before using just the selected features for the learning task. Filter methods typically rank and select features

according to univariate and multivariate measures of those features. For example, Correlation-Based Feature Selection (CFS) [59] selects feature subsets which maximize the heuristic of that subset's merit.

$$Merit_S = \frac{k \overline{r_{fc}}}{\sqrt{k + (k - 1) \overline{r_{ff}}}},$$

(2.19)